# A Modified Modulation Scheme for Three-Level Diode-Clamped Matrix Converter under Unbalanced Input Conditions

Mei Su<sup>1</sup>, Ziyi Zhao<sup>1</sup>, Hanbing Dan<sup>1\*</sup>, Tao Peng<sup>1</sup>, Yao Sun<sup>1</sup>, Ruyu Che<sup>1</sup>, Fan Zhang<sup>1</sup>, Qi Zhu<sup>1</sup>, Patrick Wheeler<sup>2</sup>

<sup>1</sup> School of Information Science and Engineering, Central South University, Changsha, Hunan 410083 China

<sup>2</sup> Department of Electrical and Electronic Engineering, University of Nottingham, Nottingham NG7 2RD, UK.

\* daniel698@sina.cn

Abstract—The three-level diode-clamped matrix converter topology has outstanding performance under ideal operating conditions. However, input disturbance can influence the waveforms at the output side of the converter due to the direct coupling between the input and output. This paper proposes a modified modulation scheme for three-level diode-clamped matrix converter during operation with unbalanced input voltages and when different transformer turns ratios are used for an isolation transformer at the input. With this modulation technique, sinusoidal and balanced output voltages are guaranteed and the input current harmonics are minimized. Experimental results are presented to demonstrate the feasibility and effectiveness of the proposed modulation scheme.

Keywords—Different transformer turns ratios of the isolation transformer, three-level diode-clamped matrix converter, unbalanced input voltages, modified modulation scheme

### 1. Introduction

Multilevel power converters [1, 2] have a number of advantages including lower output voltage distortion and semiconductor device voltage stress. These features make them very suitable for high-power, high-voltage applications, such as large variable-speed motor drives, high-voltage direct-current transmission, railway traction and manufacturing [3-7]. Matrix converters (MCs) also have advantages such as four-quadrant operation, sinusoidal input and output currents and no large energy storage elements. By combining the advantages of multilevel converters and MCs, the multilevel MCs [8-20] are receiving a lot of attention.

Lots of multilevel MC topologies have been studied, consisting of multi-modular MCs [8-12], diode-clamped MCs [13-17], and capacitor-clamped (flying capacitor) MCs [18-20]. The three-level diode-clamped matrix converter (TLDCMC) [16, 17] inherits the features of the conventional multilevel inverter and the indirect matrix converter (IMC). The phase opposite disposition (POD) modulation method and phase disposition (PD) modulation method can both be applied to the TLDCMC under the assuming ideal input voltages [16, 17]. However, in practice, the input voltages are likely to be unbalanced. Due to the lack of dc-link energy storage, the input disturbance will be transferred directly to the load, thereby influence the quality of the output waveform. Meanwhile, the input current will also become distorted.

Several strategies have been proposed to suppress the problems associated with unbalanced input voltages for low voltage MCs. The feed-forward compensation strategy was proposed in [21]. The fluctuation of virtual dc-link voltage is compensated by modifying the modulation index of inverter stage. As a result, balanced sinusoidal output currents are obtained, but the input current distortion is not considered.

Casadei et al. [22] divide the unbalanced input voltage into positive and negative sequence components and modify the input power factor angle. Experimental results were presented in [23] with nearly sinusoidal input and output currents under unbalanced input voltage. Lei et al. [24] simplify the implementation of the method in [22], and use a notch filter to obtain the expected input power factor angle. Yan et al. [25] propose two improved double line voltage synthesis strategies for MC to eliminate the input current harmonic under unbalanced condition. Li et al. [26] propose three modulation strategies to eliminate the weak input current of MC based on a mathematic construction. Rojas et al. [27] also proposed three control schemes based on the predictive control algorithms to compensate for the input voltage unbalance producing good quality input and output current waveforms. Lei et al. [28] utilize a feedback control strategy to modify input reference current. Resonant controllers are used to regulate input current and instantaneous active power, so as to directly eliminate the input current harmonics and meanwhile ensure the load absorbing constant active power under unbalanced input voltage.

For high voltage applications, the large power exaggerates the negative effects introduced by unbalanced input voltages. In three-phase systems, the harmonics will degrade the power quality and also cause disturbance to other consumers and communication equipment [29]. Obviously, the option adding large extra active power filter is often uneconomical. Satisfying load command by adopting a modified modulation scheme is a good way to eliminate the harmonics at the output of the converter. Similar to the indirect MC, this paper proposes a modified modulation scheme for the TLDCMC during operation with unbalanced input voltages and when different transformer turns ratios are used for an isolation transformer at the input. The modified modulation scheme can achieve good performance in both the input currents and output voltages. This paper contributes significant details, a full analysis and experimental results to the basic principles of this modulation method [30].

This paper is organized as follows: the converter topology is introduced in Section 2. Then, Section 3 presents the modified modulation scheme for TLDCMC during operation with unbalanced input voltages and when different transformer turns ratios are used for an isolation transformer at the input. Finally, the effectiveness of the modified modulation scheme is verified by experimental results in Section 4.

#### 2. Topology of TLDCMC

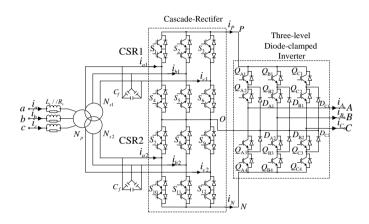

The topology of TLDCMC is shown in Fig. 1, which consists of a second-order inductive-capacitor high frequency input filter, a three-phase three-winding isolation transformer, a cascaded-rectifier and a three-level diode-clamped inverter.

Fig. 1. Topology of TLDCMC.

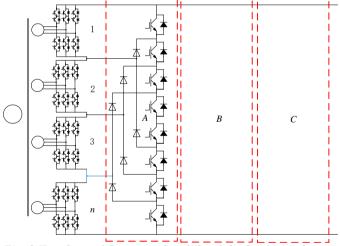

*Fig. 2 Topology of the general multilevel diode-clamped matrix converter*

The cascade rectifier consists of two bidirectional, three-phase current source rectifiers (CSRs) modules connected in series. These two CSR modules are composed of six bidirectional switch units ( $S_1$ - $S_6$  and  $S_7$ - $S_{12}$ ). Each bidirectional switch is realized by two insulated-gate bipolar transistors (IGBTs) with anti-parallel diode pairs connected to a common emitter configuration. The rectifier stage provides three output

terminals, *P*, *O* and *N*. The inverter stage is a three-level diode-clamped voltage source inverter, the value of dc-link voltage is time-varying.

This topology has following advantages:

• This topology can be extended to a general multilevel diode-clamped MC easily as shown in Fig. 2. If (n-1) bidirectional CSR modules are cascaded to construct a cascaded-rectifier that can provide n output terminals, the cascaded-rectifier would be connected to an n-level diode clamped inverter.

• Similar to the IMC, the rectifier stage and the inverter stage can be controlled independently. A similar modulation scheme can be used for TLDCMC.

• The TLDCMC can overcome the voltage rating limits of the power semiconductors for high-voltage applications and avoid the voltage balance issue associated with conventional multi-level topologies. The corresponding derivation is shown in Section 3.2.

# **3.** Modified modulation scheme under unbalanced input conditions

Modulation schemes for the TLDCMC operating under balanced input voltage conditions have been studied in [16] and [17]. In practice, the unbalanced input voltage is a potential problem. In this part, the modified modulation scheme for TLDCMC during operation with unbalanced input voltages and same transformer turns ratios is presented, firstly. The main idea of the modified modulation scheme is as follow: a modified modulation matrix for rectifier stage is given to maintain the constant average dc-link voltage, and the balanced output voltage is obtained by the normal POD method. The TLDCMC can avoid voltage balance issue associated with conventional multi-level topologies. By modifying the modulation signals in the inverter stage, the modified modulation scheme is extended to fit the TLDCMC during operation with unbalanced input voltages and when different transformer turns ratios are used for an isolation transformer at the input.

3.1. Unbalanced input voltages condition under same transformer turns ratios

Assume the primary-to-secondary turns ratios of the isolation transformer are same, the modified modulation method is presented. In addition, the sinusoidal input current is derived and maximum output voltage is analyzed.

## 3.1.1 Modified modulation matrix for rectifier stage

For the convenience, the variables in the three-phase system are represented by space vector as

$$x = \frac{2}{3} \left( x_a + x_b e^{j2\pi/3} + x_c e^{j4\pi/3} \right)$$

(1)

For the space vector  $\vec{x}$  and  $\vec{y}$ , if the space vector  $\vec{x}$  satisfy  $x_a + x_b + x_c = 0$ , the following formulation can be established

$$\frac{3}{2} \overset{\mathbf{r}}{x} \cdot \overset{\mathbf{u}}{y} = \begin{bmatrix} x_a \\ x_b \\ x_c \end{bmatrix}^T \begin{bmatrix} y_a \\ y_b \\ y_c \end{bmatrix}$$

(2)

Considering the unbalanced grid, the input voltage vector can be represented as

$$\mathbf{U}_{in} = V_p e^{j(\omega_i t + \theta_p)} + V_n e^{j(-\omega_i t + \theta_n)}$$

(3)

where  $V_p$  and  $V_n$  are the amplitudes of positive and negative sequence input phase voltage vectors, respectively.  $\theta_p$  and  $\theta_n$ are the initial angle of positive and negative sequence input phase voltage vectors, respectively.  $\omega_i$  is the angular frequency of the input phase voltage.

The balanced output voltage vector and output current vector are assumed to be:

$$\begin{cases} \mathbf{u}\mathbf{u}^{\mathbf{u}}_{out} = V_{om}e^{j(\omega_{o}t + \theta_{o})} \\ \mathbf{u}\mathbf{r}_{out} = I_{om}e^{j(\omega_{o}t + \theta_{o} - \psi_{o})} \end{cases}$$

(4)

where  $\psi_o$  is the angle that the load current lags the output voltage. Vom and Iom are the amplitudes of output voltage and output current vectors.  $\theta_o$  is the initial angle of output phase voltage vectors.  $\omega_o$  is the angular frequency of the output phase voltage.

Then the output power can be calculated as

$$P_o = \frac{3}{2} \underbrace{V_{out}}_{V_{out}} \cdot \underbrace{i_{out}}_{out} \tag{5}$$

In addition, the input power can be expressed by

$$P_{in} = \frac{3}{2} \frac{\mathbf{u}\mathbf{r}}{V_{in}} \cdot \frac{\mathbf{u}\mathbf{r}}{i_{in}} \tag{6}$$

According to active power balance

$$P_o = P_{in} \tag{7}$$

The rectifier modulation matrix is defined as  $\overline{M_{REC}}$  for current source rectifier. Assume the  $\overline{M_{REC}}$  as

$$M_{REC} = M_p e^{j(\omega_l t + \theta_p - \psi_p)} + M_n e^{j(-\omega_l t + \theta_n - \psi_n)}$$

(8)

where  $\psi_p$  and  $\psi_n$  are the power factor angle of positive and negative sequence input voltage vectors, respectively.  $M_p$  and  $M_n$  are the modulation factors of positive and negative sequence input voltage vectors, respectively.

The average dc-link voltage  $V_{dc}$  of the cascaded-rectifier can be given by

$$V_{dc} = 2V_{po} = 2V_{on} = \frac{{}_{3N_s} Ur}{N_p} V_{in} \cdot M_{REC}$$

(9)

where  $V_{po}$  and  $V_{on}$  are the average dc-link voltage of rectifier1 and rectifier2, respectively.  $N_p/N_s$  is the primary-to-secondary turns ratios of the isolation transformer. And it meets  $\frac{N_p}{N_{s1}} = \frac{N_p}{N_{s2}} = \frac{N_p}{N_s}$ . Combining (3), (8) and (9), the average dc-link voltage of

cascaded-rectifier can be expressed as

$$V_{dc} = \frac{{}^{3N_s}}{{}^{N_p}} \Big\{ V_p M_p \cos \psi_p + V_n M_n \cos \psi_n + V_p M_n \cos(2\omega_i t + \theta_p - \theta_n + \psi_n) + (10) \\ V_n M_p \cos(-2\omega_i t + \theta_n - \theta_p + \psi_p) \Big\}$$

As shown in (10), the value of average dc-link voltage consists of a dc term and a second order harmonic. Since the second

order term brings low order harmonics to both sides of the converter, the modulation matrix has to be carefully selected for purposes of elimination. The following equations can be obtained

$$\begin{cases} M_p V_n = M_n V_p \\ \psi_p = \pi - \psi_n = \varphi_i \end{cases}$$

(11)

where  $\varphi_i$  is the power factor angle of the unbalanced input voltage.

Then, the modified modulation matrix can be described by

$$M_{REC} = M_p \left( e^{j(\omega_i t + \theta_p - \varphi_i)} - \frac{V_n}{V_p} e^{j(-\omega_i t + \theta_n + \varphi_i)} \right)$$

(12)

To make full use of the input voltage and meet  $|\overline{M_{REC}}| < 1$ , the modified modulation matrix is chosen as follow

$$\overset{\textbf{uture}}{M}_{REC} = \frac{V_p e^{j(\omega_l t + \theta_p - \varphi_l)} - V_n e^{j(-\omega_l t + \theta_n + \varphi_l)}}{V_p + V_n}$$

(13)

Then the average dc-link voltage can be calculated as

$$V_{dc} = 2V_{po} = 2V_{on} = \frac{3N_s}{N_p} (V_p - V_n) \cos \varphi_i$$

(14)

The modified rectifier modulation matrix can also be used in all n-1 CSR modules of general multilevel diode-clamped MC. As a result, it will yield *n* levels for the dc-link voltage.

#### 3.1.2 Modulation for inverter stage

When the number of inverter levels increases, it is more difficult to realize the modulation of the inverter stage using the space vector pulse width modulation (SVPWM). Thus, the carrier modulation scheme is considered for inverter stage due to the simple implement scheme. For simplicity, the POD method is adopted in this paper, but the technique can be applied to other modulation methods.

Assume that the desired output phase voltages are

$$\begin{cases} u_A = \sqrt{2}U_{oRMS}\cos(\varphi_A) \\ u_B = \sqrt{2}U_{oRMS}\cos(\varphi_B) \\ u_C = \sqrt{2}U_{oRMS}\cos(\varphi_C) \end{cases}$$

(15)

where  $U_{oRMS}$  is the root mean square (RMS) of the output phase voltage respectively.  $\varphi_A$ ,  $\varphi_B$  and  $\varphi_C$  denote the phase angle of output voltages, respectively.

To maximize the utilization of dc-link voltage, the zero-sequence  $u_{NO}$  is considered, the modulation signals  $u_{iO}$ are as follow

$$u_{io} = u_i + u_{NO}, \ i \in \{A, B, C\}$$

(16)

where the zero-sequence  $u_{NO}$  is chosen by

$$u_{NO} = -\frac{\min(u_A, u_B, u_C) + \max(u_A, u_B, u_C)}{2}$$

(17)

Normalizing the  $u_{io}$ , the modulation signals are obtained as

$$\overline{u}_{io} = 2\frac{u_{io}}{V_{dc}} \tag{18}$$

The modulation signals can be normalized as

$$d_{ip} = \begin{cases} \frac{u_{io}}{V_{po}}, & when \ u_{io} \ge 0\\ 0, & when \ u_{io} \le 0 \end{cases}$$

(19)

$$d_{in} = \begin{cases} 0, & when \ u_{io} \ge 0\\ \frac{-u_{io}}{V_{on}}, & when \ u_{io} \le 0 \end{cases} i \in \{A, B, C\}$$

(20)

where  $d_{ip}$  denotes the duty cycle of the switching state P ( $Q_{i1}$  and  $Q_{i2}$  are ON, while  $Q_{i3}$  and  $Q_{i4}$  are OFF.);  $d_{in}$  denotes the duty cycle of the switching state N ( $Q_{i1}$  and  $Q_{i2}$  are OFF, while  $Q_{i3}$  and  $Q_{i4}$  are ON.).

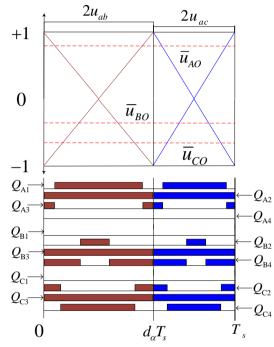

Assume that the input line-to-line voltage of rectifier stage is  $u_{ab}$  and  $u_{ac}$  during the modulation period  $T_s$ . The duty ratio of the active vector  $u_{ab}$  is  $d_{\alpha}$ . The POD method for the inverter stage can be implemented as shown in Fig. 3.

Fig. 3. POD method for inverter stage.

By adjusting the rectifier modulation matrix, the method can suppress the effect introduced by unbalanced inputs, which is a simple and easy way to implement. Since the limitation of inverter modulation index, the maximum amplitude of output phase voltage is

$$\left(U_{om}\right)_{\max} = \frac{\sqrt{3}N_s}{N_p} (V_p - V_n) \cos \varphi_i \tag{21}$$

If the input voltage is seriously unbalanced, the maximum amplitude of output voltage will decrease. If the amplitudes of positive and negative sequence input phase voltage vectors are equal, the maximum amplitude of output voltage will be zero and the desired output voltage can't be synthesized.

For the *n*-level inverter, the multicarrier-based method with *n*-1 carriers should be applied.

3.1.3 Input current derivations

As for the unbalanced input voltage, the input currents can be derived as

$$\hat{i}_{i} = \frac{N_{s}}{N_{p}} M_{REC} \left( i_{P} - i_{N} \right)$$

(22)

where  $\vec{l_i}$  is the space vectors of source current  $\vec{l_i}$ .

The average dc-link current in a switching period can be expressed as follow

$$\begin{cases} i_{P} = d_{Ap}i_{A} + d_{Bp}i_{B} + d_{Cp}i_{C} \\ i_{N} = d_{An}i_{A} + d_{Bn}i_{B} + d_{Cn}i_{C} \\ i_{O} = -(i_{P} + i_{N}) = 0 \end{cases}$$

(23)

The neutral point current  $i_0$  equals zero when the dc-link voltage is balanced. Then, after some manipulations with (14), (19), (20), and (23), the following equation can be obtained

$$i_p - i_N = \frac{2P_o N_p}{3N_s (V_p - V_n) \cos \varphi_i}$$

(24)

where  $P_o = u_A i_A + u_B i_B + u_C i_C$  represents the output active power.

Combining (13), (22) and (24), the input current space vector can be derived as

$$\mathbf{r}_{i} = \frac{2P_{o}\left(V_{p}e^{j(\omega_{i}t+\theta_{p}-\varphi_{i})}-V_{n}e^{j(-\omega_{i}t+\theta_{n}+\varphi_{i})}\right)}{3\cos(\varphi_{i})\left(V_{p}^{2}-V_{n}^{2}\right)}$$

(25)

If  $P_o$  is constant, the input current  $i_i$  is sinusoidal and unbalanced with the proposed modulation scheme under unbalanced input voltages according to (25).

3.2 Unbalanced input voltages condition under different transformer turns ratios

The TLDCMC does not require balance of the dc-link voltage. In fact, there is no constraint for same transformer turns ratios of the isolation transformer. The modified modulation scheme for same transformer turns ratios in Section 3.1 is extended in this part. By modifying the modulation signals of the inverter stage, the modified modulation scheme is extended to fit the TLDCMC during operation with unbalanced input voltages and when different transformer turns ratios are used for an isolation transformer at the input. The desired output voltage and input current are obtained.

#### 3.2.1 Output voltage derivations

Considering the same modulation matrix as (13) at rectifier stage and different transformer turns ratios for an isolation transformer at the input  $(\frac{N_p}{N_{s1}} \neq \frac{N_p}{N_{s2}})$ , the average dc-link voltage of the two rectifiers can be calculated as

$$\begin{cases} V_{po} = \frac{3N_{s1}}{2N_p} (V_p - V_n) \cos \varphi_i \\ V_{on} = \frac{3N_{s2}}{2N_p} (V_p - V_n) \cos \varphi_i \end{cases}$$

(26)

The average dc-link voltages of the two rectifiers are unequal. In order to get the balanced output voltage, the load side switching function is adjusted to compensate dc-link voltage. To maximize the utilization of dc-link voltage, the modulation signals are given by

$$u_{io} = u_i + u_{NO1} + u_{NO2}, \quad i \in \{A, B, C\}$$

(27)

where  $u_{io}$  are the modulation signals and  $u_{NO1}$ ,  $u_{NO2}$  are the zero-sequence signals, respectively. And the zero-sequence signals are selected as follow

$$\begin{cases}

u_{NO1} = \frac{V_{po} - V_{on}}{2} \\

u_{NO2} = -\frac{\min(u_A, u_B, u_C) + \max(u_A, u_B, u_C)}{2}

\end{cases}$$

(28)

The modulation signals can be normalized as (19) and (20). Then, the balanced output voltage can be obtained. By adding additional zero sequence components  $u_{NO1}$  to the inverter modulation signals, the method can suppress the effect introduced by different transformer turns ratios of the isolation transformer and obtain the desired output voltage as the equal situation.

From (26) and (28), when the transformer turns ratios are same, the zero-sequence signal  $u_{NO1}$  equals zero and the modulation signals become exactly same as (16).

Due to the limitation of inverter modulation index, the maximum amplitude of output phase voltage is

$$(U_{om})_{\max} = \frac{\sqrt{3}(N_{s1} + N_{s2})}{2N_p} (V_p - V_n) \cos \varphi_i$$

(29)

when the transformer turns ratios are equal, (29) becomes (21).

#### 3.2.2 Input current derivations

As for the different transformer turns ratios, the average dc-link current in a switching period can be expressed as follow

$$\begin{cases} i_{P} = d_{AP}i_{A} + d_{BP}i_{B} + d_{CP}i_{C} \\ i_{N} = d_{An}i_{A} + d_{Bn}i_{B} + d_{Cn}i_{C} \\ i_{O} = -\left(\left(\frac{u_{AO}}{V_{po}} - \frac{u_{AO}}{V_{on}}\right)i_{A} + \left(\frac{u_{BO}}{V_{po}} - \frac{u_{BO}}{V_{on}}\right)i_{B} \right) \\ + \left(\frac{u_{CO}}{V_{po}} - \frac{u_{CO}}{V_{on}}\right)i_{C} \end{cases}$$

(30)

The neutral point current  $i_0$  is not zero when the dc-link voltage  $V_{po}$  is not equal to  $V_{on}$ . Then, after some manipulations with (15), (19), (20), (26), (27), (28) and (30), the following equation could be obtained

$$\frac{N_{s1}}{N_p}i_p - \frac{N_{s2}}{N_p}i_N = \frac{2P_o}{3(V_p - V_n)\cos\varphi_i}$$

(31)

where  $P_o = u_A i_A + u_B i_B + u_C i_C$  represents the output active power.

The input current space vector  $\vec{\iota}_i$  could be expressed as follows

$$\vec{i}_{i} = M_{REC} \left( \frac{N_{s1}}{N_{p}} \vec{i}_{p} - \frac{N_{s2}}{N_{p}} \vec{i}_{N} \right)$$

(32)

After some manipulations with (13), (31) and (32), the input current can be written as

$$\mathbf{r}_{i} = \frac{2P_{o}\left(V_{p}e^{j(\omega_{i}t+\theta_{p}-\varphi_{i})} - V_{n}e^{j(-\omega_{i}t+\theta_{n}+\varphi_{i})}\right)}{3\cos(\varphi_{i})\left(V_{p}^{2}-V_{n}^{2}\right)}$$

(33)

Compared (33) with (25), the input current is same and not affected by the different transformer turns ratios.

Through the analysis of this section, the TLDCMC can work under the situation that  $V_{po}$  is not equal to  $V_{on}$ . The desired output voltage and input current can also be obtained. The modified modulation scheme is fit for TLDCMC during operation with unbalanced input voltages and when different transformer turns ratios are used for an isolation transformer at the input.

#### 4. Experimental results

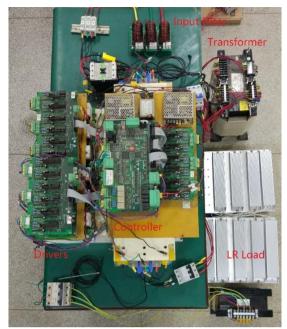

To verify the modified modulation scheme, a low-voltage experimental prototype is implemented as shown in Fig. 4. The related component parameters are listed in Table.1. The cascaded-rectifier uses the SVPWM method and the POD method is employed in the three level diode clamped inverter. In addition, with an appropriate switching sequence, the zero current commutation is implemented. In the cascaded-rectifier, the IGBT module FF300R12KT3 E is used for the four quadrant power switches. The IGBT module F3300R12ME4 B23 and F3300R12ME4 B23 are connected in series as the one phase leg of the three level diode clamped inverter. The voltage stresses of the switches are related to the input line-to-line peak voltage of secondary transformer. The input voltage and the output current can be measured through the sensor circuits. A floating-point digital signal processor (DSP, TMS320F28335) and a field programmable gate array (FPGA, EP2C8J144C8N) are equipped with the controller board. The desired duty ratios of the switches are calculated in DSP and transmitted to FPGA. Then, the desired switching sequences and commutation process are implemented in FPGA.

The following three conditions are experimentally tested to verify the modified modulation scheme. The *Condition I* is experimentally tested to verify that the TLDCMC can avoid the voltage balance issue associated with conventional multi-level topologies. In practical application, to maintain the same voltage stress for the semiconductor device at inverter stage, the transformer turns ratios of the isolation transformer are usually same. Thus, the *Condition II* and *Condition III* with same transformer turns ratios are considered.

*Condition I*: The converter is fed by balanced input voltage 220V/50Hz (RMS). The transformer used for experiments has a fixed primary to secondary ratio of 380:200 and 380:100 respectively.

*Condition II*: The converter is fed by balanced input voltage 115V/50Hz (RMS). The phase shifts among three input phase voltages are 120 degrees. The transformer used for experiments has a fixed primary to secondary ratio of 380:200.

*Condition III*: The a-phase and b-phase input voltages are 115V/50Hz (RMS), while c-phase input voltage is 81V/50Hz (RMS). The phase shifts among three input phase voltages are

120 degrees. The transformer used for experiments has a fixed primary to secondary ratio of 380:200.

*Fig. 4. The experimental prototype of TLDCMC.* Table 1. Component parameters of experimental prototype

| Parameters                                  | Value    |  |  |

|---------------------------------------------|----------|--|--|

| Switching frequency $(f_s)$                 | 5kHz     |  |  |

| Input filter inductor ( $L_s$ )             | 0.6mH    |  |  |

| Input filter capacitor ( $C_{fl}, C_{f2}$ ) | 22uF     |  |  |

| Damping resistor $(R_s)$                    | 9Ω       |  |  |

| Load resistor $(R)$                         | 13.33Ω   |  |  |

| Load inductor ( $L_o$ )                     | 6mH      |  |  |

| Current sensor                              | LT308-S7 |  |  |

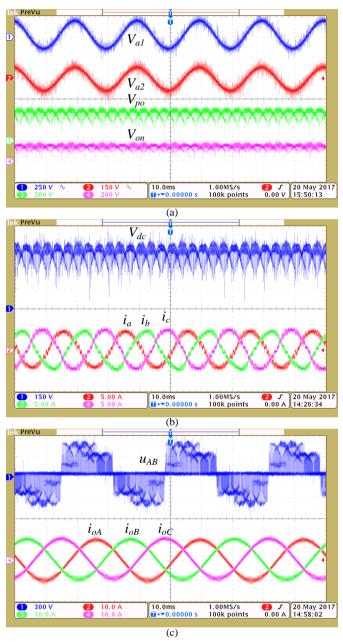

Fig. 5 shows the experimental waveforms under *Condition I*, when the amplitude and frequency of desired output phase voltage are set to 140V/30Hz. As seen, the nearly sinusoidal input currents are achieved when the isolation transformer has different transformer turns ratios. As for the conventional three-level diode clamped inverter, the voltages of the two dc-link capacitors should be controlled to achieve equal voltage. However, the TLDCMC can avoid the voltage balance issue. As seen in Fig. 4 (a), the dc-link voltages of two rectifiers are different because of the different transformer turns ratios of the isolation transformer. However, the balanced output currents are obtained as seen in Fig. 4 (c). The output line-to-line voltage is characterized by five levels.

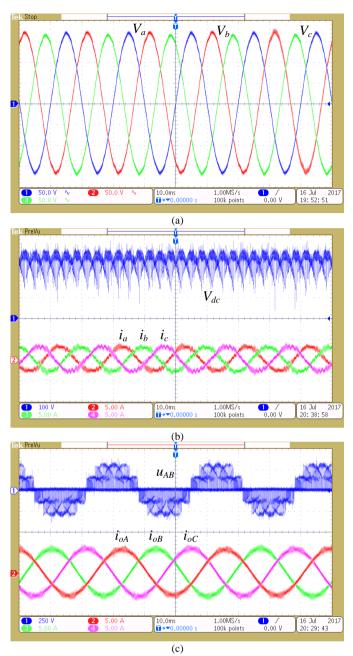

Fig. 6-7 shows the experimental waveforms under *Condition II*, when the amplitude and frequency of desired output phase voltage are set to 80V/30Hz and 80V/60Hz, respectively. As seen, the balanced input currents and output currents are achieved when the input voltages are balanced. The input and output currents are nearly sinusoidal. The distortion of input currents is mainly caused by the dead-time, device voltage drop, distorted no-load current in the transformer, and so on. The related total harmonic distortion

(THD) values of input and output currents are listed in Table 2.

Fig. 5. The experimental waveforms with a reference output phase voltage of 140V/30Hz under Condition I.

(a) Ch1: the a1-phase input voltage of the secondary transformer winding1  $V_{a1}$ , Ch2: the a2-phase input voltage of the secondary transformer winding2  $V_{a2}$ , Ch3: the average dc-link voltage of rectifier1  $V_{po}$  Ch4: the average dc-link voltage of rectifier2  $V_{on}$

(b) Ch1: the dc-link voltage  $V_{dc}$ , Ch2: the a-phase input current, Ch3: the b-phase input current, Ch4: the c-phase input current.

(c) Ch1: the output line-to-line voltage  $U_{AB}$ , Ch2: the A-phase output current, Ch3: the B-phase output current, Ch4: the C-phase output current.

Fig. 6. The experimental waveforms with a reference output phase voltage of 80V/30Hz under Condition II.

(a) Ch1: the input phase voltage  $V_{a}$ , Ch2: the input phase voltage  $V_{b}$ , Ch3: the input phase voltage  $V_{c}$ .

(b) Ch1: the dc-link voltage  $V_{dc}$ , Ch2: the a-phase input current, Ch3: the b-phase input current, Ch4: the c-phase input current.

(c) Ch1: the output line-to-line voltage  $U_{AB}$ , Ch2: the A-phase output current, Ch3: the B-phase output current, Ch4: the C-phase output current.

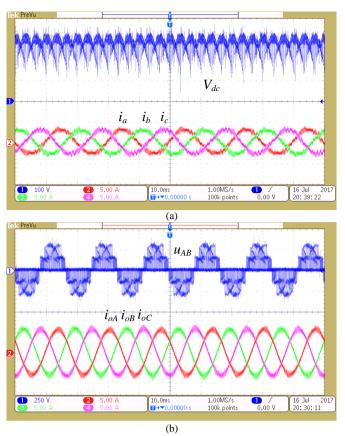

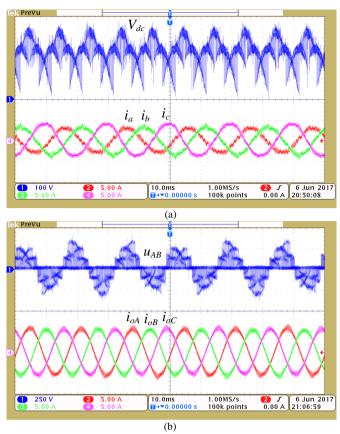

Fig. 7. The experimental waveforms with a reference output phase voltage of 80V/60Hz under Condition II.

(a) Ch1: the dc-link voltage  $V_{dc}$ , Ch2: the a-phase input current, Ch3: the b-phase input current, Ch4: the c-phase input current.

(b) Ch1: the output line-to-line voltage  $U_{AB}$ , Ch2: the A-phase output current, Ch3: the B-phase output current, Ch4: the C-phase output current.

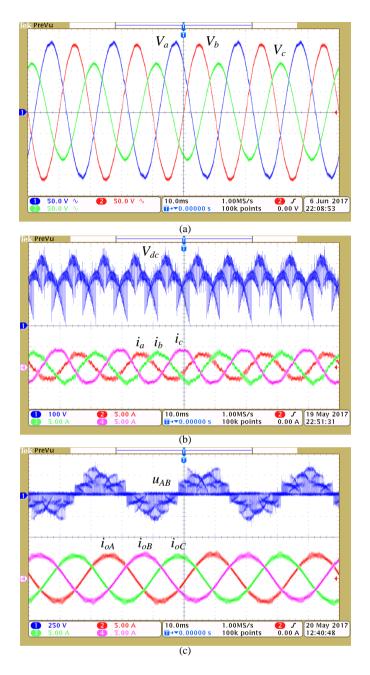

Fig. 8-9 shows the experimental waveforms under *Condition III*, when the amplitude and frequency of desired output phase voltage are set to 80V/30Hz and 80V/60Hz, respectively. As seen, the nearly sinusoidal input currents and output currents are achieved when the input voltages are unbalanced. The related THD values of input and output currents are listed in Table 2. Comparing the output current waveforms under *Condition II* and *Condition III*, there are no obvious difference between them. The modified modulation scheme is verified by the experimental results.

Fig. 8. The experimental waveforms with a reference output phase voltage of 80V/30Hz under condition III.

(a) Ch1: the input phase voltage  $V_a$ , Ch2: the input phase voltage  $V_b$ , Ch3: the input phase voltage  $V_c$ .

(b) Ch1: the dc-link voltage  $V_{dc}$ , Ch2: the a-phase input current, Ch3: the b-phase input current, Ch4: the c-phase input current.

(c) Ch1: the output line-to-line voltage  $U_{AB}$ , Ch2: the A-phase output current, Ch3: the B-phase output current, Ch4: the C-phase output current.

Fig. 9. The experimental waveforms with a reference output phase voltage of 80V/60Hz under Condition III.

(a) Ch1: the dc-link voltage  $V_{dc}$ , Ch2: the a-phase input current, Ch3: the b-phase input current, Ch4: the c-phase input current.

(b) Ch1: the output line-to-line voltage  $U_{AB}$ , Ch2: the A-phase output current, Ch3: the B-phase output current, Ch4: the C-phase output current.

Table 2. THD values of the input and output currents under *Condition II* and *III*

| containen ir and iri |                |                |                |       |                |                |  |  |

|----------------------|----------------|----------------|----------------|-------|----------------|----------------|--|--|

| Condition (%)        | i <sub>a</sub> | i <sub>b</sub> | i <sub>c</sub> | $i_A$ | i <sub>B</sub> | i <sub>c</sub> |  |  |

| <i>II</i> -80V/30Hz  | 12.32          | 12.25          | 12.37          | 4.49  | 4.52           | 4.54           |  |  |

| <i>II</i> -80V/60Hz  | 12.12          | 12.58          | 13.50          | 2.90  | 3.05           | 2.94           |  |  |

| III-80V/30Hz         | 13.00          | 11.92          | 8.87           | 4.87  | 4.93           | 4.80           |  |  |

| III-80V/60Hz         | 13.03          | 11.50          | 8.65           | 3.82  | 3.80           | 3.73           |  |  |

#### 5. Conclusion

This paper has presented the implementation of a modified modulation scheme for the TLDCMC during operation with unbalanced input voltages and when different transformer turns ratios are used for an isolation transformer at the input. The good performance of input and output currents is obtained. The modified modulation scheme is also applicable to the generalized multilevel diode-clamped matrix converter under unbalanced input voltage. The experimental results validate the correctness and feasibility of the proposed modulation method and the feature that the TLDCMC can avoid the voltage balance issue associated with multi-level topologies. Moreover, the modified modulation scheme can be also used under ideal operating conditions.

#### 6. References

- Lai, J.S., Peng, F.Z.: 'Multilevel converters. a new breed of power converters', IEEE Trans. Ind. Appl.,1996, 32, (3), pp. 509-517

- [2] Gnanasambandam, K., Rathore, A.K., Edpuganti, A., et al.: 'Current-fed multilevel converters: an overview of circuit topologies, modulation techniques, and applications', IEEE Trans. on Power Electronics, 2017, 32, (5), pp. 3382-3401

- [3] Rodriguez, J., Bernet, S., Wu, B., et al.: 'Multilevel voltage-source-converter topologies for industrial medium-voltage drives', IEEE Trans. Ind. Electron., 2007, 54, (6), pp.2930-2945

- [4] Kouro, S., Malinowski, M., Gopakumar, K., et al.: 'Recent advances and industrial applications of multilevel converters'. IEEE Trans. Ind. Electronics., 2010, 57, (8), pp. 2553-2580

- [5] Brando, G., Dannier, A., Pizzo, A.D., et al.: 'Generalised look-up table concept for direct torque control in induction drives with multilevel inverters'. IET Electric Power Applications, 2015, 9, (8), pp. 556-567

- [6] Novakovic, B., Nasiri, A.: 'Modular multilevel converter for wind energy storage applications', IEEE Trans. on Industrial Electronics, 2017, 64, (11), pp. 8867-8876

- [7] Li, B., Zhou, S., Xu, D., et al.: 'A hybrid modular multilevel converter for medium-voltage variable-speed motor drives', IEEE Transactions on Power Electronics, 2017, 32, (6), pp. 4619-4630

- [8] Change, J.: 'Modular AC-AC variable voltage and variable frequency power converter system and control', US Patent 5909367, June 1999

- [9] Jun, K., Yamamoto, E., Ikeda, M., et al.: 'Medium-Voltage Matrix Converter Design Using Cascaded Single-Phase Power Cell Modules', IEEE Trans. Ind. Electron, 2011, 58, (11), pp.5007-5013

- [10] Wang, J., Wu, B., Xu, D., et al.: 'Indirect Space-vector-based modulation techniques for high-power multimodular matrix converters', IEEE Trans. Ind. Electron, 2013, 60, (8), pp.3060-3071

- [11] Sun, Y., Xiong, W., Su, M., et al.: 'Carrier-based modulation strategies for multi-modular matrix converters', IEEE Trans. on Industrial Electronics, 2016, 63, (3), pp. 1350-1361

- [12] Sun, Y., Xiong, W., Su, M., et al.: 'modulation strategies based on mathematical construction method for multi-modular matrix converter', IEEE Transactions on Power Electronics, 2016, 31, (8), pp. 5423-5434.

- [13] Kolar, J.W., Schafmeister, F., Round, S. D., et al.: 'Novel three-phase AC–AC sparse matrix converters', IEEE Trans. on Power Electronics, 2007, 22, (5), pp. 1649-1661

- [14] Poh, C.L., Blaabjerg, F., Feng, G., et al.: 'Pulsewidth modulation of neutral-point-clamped indirect matrix converter', IEEE Trans. Industry Application, 2008, 44, (6), pp. 1805-1814

- [15] Meng, Y.L., Wheeler, P., Klumpner, C.: 'Space-vector modulated multilevel matrix converter', IEEE Tran. Industrial Electronics, 2010, 57, (10), pp.3385-3394

- [16] Dan, H., Peng, T., Su, M. Yao Sun, et al.: 'Implementation of phase disposition modulation method for the three-level diode-clamped matrix

converter', IET Power Electronic, 2015, 8, (11), pp. 2107-2114

- [17] Sun, Y., Xiong, W., Su, M., et al.: 'Topology and modulation for a new multilevel diode-clamped matrix converter', IEEE Trans. on Power Electronics, 2014, 29, (12), pp. 6352-6360

- [18] Shi, Y., Yang, X., He, Q., et al.: 'Research on a novel capacitor clamped multilevel matrix converter', IEEE Trans. Power Electronics, 2005, 20, (5), pp.1055-1065

- [19] Xu L., Clare, J.C., Wheeler, P., et al.: 'Capacitor clamped multilevel matrix converter space vector modulation', IEEE Trans. on Industrial Electronics, 2012, 59, (1), pp. 105-115

- [20] Qiu, L., Xu, L., Wang, K., et al.: 'Research on output voltage modulation of a 5-level matrix converter', IEEE Transactions on Power Electronics, 2017,32, (4), pp. 2568-2583

- [21] Nielsen, P., Blaabjerg, F. and Pedersen, J. K.: 'Space vector modulated matrix converter with minimized number of switchings and a feedforward compensation of input voltage unbalance', Proceedings of International Conference on Power Electronics, Drives and Energy Systems for Industrial Growth, New Delhi, 1996, 2, pp. 833-839

- [22] Casadei, D., Serra, G., Tani, A.: 'Reduction of the input current harmonic content in matrix converters under input/output unbalance', IEEE Transactions on Industrial Electronics, 1998, 45, (3), pp. 401-411

- [23] Blaabjerg, F., Casadei, D., Klumpner, C., et al.: 'Comparison of two current modulation strategies for matrix converters under unbalanced input voltage conditions', IEEE Trans. on Industrial Electronics, 2002, 49, (2), pp. 289-296

- [24] Lei, J., Zhou, B., Bian, J., et al.: 'A simple method for sinusoidal input currents of matrix converter under unbalanced input voltages', IEEE Transactions on Power Electronics, 2016, 31, (1), pp. 21-25

- [25] Yan, Y., An, H., Shi, T., et al.: 'Improved double line voltage synthesis of matrix converter for input current enhancement under unbalanced power supply', IET Power Electronics, 2013, 6, (4), pp. 798-808

- [26] Li, X., Su, M., Sun, Y., et al.: 'Modulation strategies based on mathematical construction method for matrix converter under unbalanced input voltages', IET Power Electronics, 2013, 6, (3), pp. 434-445

- [27] Rojas, C., Rivera, M., Rodriguez, J., et al.: 'Predictive control of a direct matrix converter operating under an unbalanced ac source', IEEE International Symposium on Industrial Electronics, 2010, pp. 3159-3164

- [28] Lei, J., Zhou, B., Bian, J., et al.: 'Feedback Control Strategy to Eliminate the Input Current Harmonics of Matrix Converter Under Unbalanced Input Voltages', IEEE Transactions on Power Electronics, 2017, 32, (1), pp. 878-888

- [29] Singh, B., Al-Haddad, K., Chandra, A.: 'A review of active filters for power quality improvement', IEEE Transactions on Industrial Electronics, 1999, 46, (5), pp. 960-971

- [30] Peng, T., Che, R., Dan, H., Sun, Y.: 'Investigation of three-level diode-clamped matrix converter under unbalanced input voltages', Conference of Chinese Automation Congress, 2015