# Experimental Study of the Short-Circuit Performance for a 600V Normally-Off p-Gate GaN HEMT

Thorsten Oeder Robert Bosch Center for Power Electronics Power Electronics, Machines and Control Group Chair of Energy Conversion Reutlingen University Reutlingen, GERMANY thorsten.oeder@student.reutlingen-university.de

Alberto Castellazzi University of Nottingham Nottingham, UNITED KINGDOM alberto.castellazzi@nottingham.ac.uk

Martin Pfost TU Dortmund University Dortmund, GERMANY martin.pfost@tu-dortmund.de

Abstract-In this paper, the short-circuit robustness of a normally-off GaN HEMT is investigated in relation to applied bias conditions and pulse duration. The results align with previous studies on normally-on devices in highlighting an electrical type of failure. Here, however, the relevance of the specific gate-drive circuit design and corresponding device operational conditions is demonstrated. A gate-bias dependence (GBD) of the failure, correlated to the applied drain-source voltage, is introduced as a novel specific feature for the p-Gate type device.

Keywords-Short-Circuit, GaN, HEMT, Normally-Off, p-Gate, Gate-Bias Dependence.

## I. INTRODUCTION

Semiconductor devices with higher efficiency and reliability are significant milestone for power electronic applications (PEA) in the recent decade. Therefore, the high electron mobility transistor (HEMT), which is a wide band gap (WBG) semiconductor based on an AlGaN/GaN heterojunction, exhibits a promising solution. The unique functionality and characteristics of a GaN HEMT, in comparison to a Si MOSFET or IGBT device, lead to several advantages in the application. On the other hand, in most PEAs the switching devices are required to exhibit a normally-off operation. The usage of insulated- or p-doped gates (p-gate) [1] is one of the key technological solutions to achieve that.

In typical PEAs, a number of overload operational conditions have to be considered to ensure the device- and system/circuit robustness. Typically, this conditions are managed by system-level failure-detection and shut-down mechanisms to avoid destructions. Therefore, a crucial device withstand capability is required, to guarantee their intervention. The shortcircuit (SC) robustness is a very important feature of power transistors, strictly required by a number of applications (e.g., motor drives). The common minimum requirement is to withstand a short-circuit with 50% of the maximum breakdownvoltage for an SC duration of 10  $\mu s$ . During an SC the device has to be capable of a high power dissipation, that eventually leads to an excessive self-heating related failure. A previous publication of normally-on GaN HEMT SC robustness [2] concluded the failure to be an electrical effect rather than an impact of a thermal issue. It is predicted, that the electrical impact occurs due to an accumulation of holes under the gate, which generates localised high electric fields and causes premature breakdown. Furthermore, the study determined a dependency of the time to failure, which is correlated to the gate-bias.

In this paper, a comprehensive experimental study of a normally-off p-gate HEMT is carried out. The test set-up is presented in chapter II and therefore the impact on the SC behaviour in chapter III. The SC robustness is investigated and presented according to the applied drain-source voltage in chapter IV and the SC duration in chapter V. Furthermore, during the study a variation of the gate-bias occurred, which correlates to the drain-source voltage. The characteristic and impact of this gate-bias dependence (GBD) is as a novelty introduced in chapter VI

#### II. MEASURMEMENT SET-UP

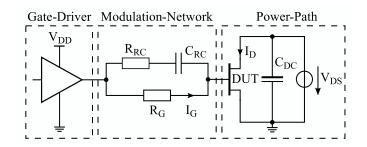

To determine the SC capability of the device, a measurement set-up composed of three major parts is used, as illustrated in Fig. 1. The SC duration can be adjusted by applying a voltage-pulse of a variable time  $(t_{SC})$  on the gatedriver that further transmits an equivalent power-pulse to the gate for biasing the DUT in on-state. Feedback related effects during the SC failure can lead to driver destruction, therefore the gate-loop is galvanic (optical) decoupled. The device under test (DUT) is low inductive linked with an external source and interconnected stabilisation capacitor in the power-path. Hence, the drain-source voltage  $V_{\rm DS}$  can be assumed constant due to the large capacitance value.

Driving a p-gate HEMT features the existence of an onstate forward gate-current  $I_{\rm G}$ . The amount of the current

Fig. 1: Test set-up, composed of: a galvanic (optical) decoupled gate-driver, a modulation-network of the gate-signal (common used in p-gate GaN HEMT applications), and a power-path with the device under test (DUT)  $I_{\rm G}$  can be adjusted with an appropriate gate-resistance  $R_{\rm G}$ . Consequently, the gate-source voltage  $V_{\rm GS}$  is set by  $I_{\rm G}$  with the equivalent voltage drop over  $R_{\rm G}$ . Therefore, as part of the gate-drive circuit, a modulation-network is used. This topology ensures a, with the usage in PEAs, comparable gatebias condition of the SC behaviour. Furthermore, the network provides optimised transient on- and off-state bias conditions of the DUT which are illustrated in Fig. 2 (bottom).

## III. SC BEHAVIOUR AND TEST CONDITIONS

Various influences on the SC behaviour, related to the impact of the gate-drive circuit, can be captured. In the following, the relations are exemplary described, together with the extent of variation in the gate-drive circuit.

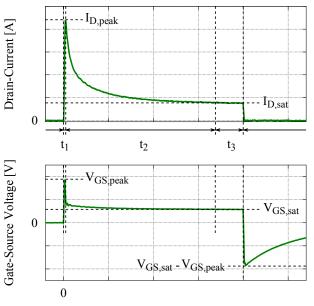

The waveform of the drain-current  $I_{\rm D}$  is depicted in Fig. 2 (top), with the respective  $V_{GS}$  in Fig. 2 (bottom), serving as the impact exemplification. In the first time interval  $t_1$  of the SC, a steep rise of the current  $I_D$  occurs. The slope is mainly determined by the applied voltage  $V_{DS}$  and the parasitic inductance of the SC loop. The p-gate structurally lacks a capacitive nature, therefore  $V_{GS}$  is equal to the value of the drive-voltage  $V_{GS,peak} = V_{DD}$ . During the second time interval  $t_2$  the voltage converge to its saturation value  $V_{\text{GS,sat}}$ , in accordance to the functionally of the gate-drive circuit. Therefore, the current  $I_D$  tends to decrease, which is further gained due to the impact of the self-heating. The issue of selfheating is related to an excessive power-dissipation and occurs as a thermal mobility degeneration [3]. In the last interval  $t_3$ , the temperature within the device reaches a stable value, which leads to a respective saturation of the current  $I_{D,sat}$ .

To cover the impact of the gate-drive circuit, a variation of test conditions is carried out. These test conditions are

Time [µs]

Fig. 2: Drain-current vs. time (top), gate-source voltage vs. time (bottom). Exemplary waveforms of the SC behaviour, within the characteristics according to the gate-drive circuit.

TABLE I: Variation of test conditions and results of failure related SC limitation. The failure-time is determined with  $V_{\text{DS}} = 300 \text{ V}$  and the failure-voltage with  $t_{\text{SC}} = 10 \ \mu s$ .

| Conditon        |                           | А   | В     | С    | D    |

|-----------------|---------------------------|-----|-------|------|------|

| Gate-resistance | $R_G \left[\Omega\right]$ | 470 | 4.7 k | 980  | var. |

| Drive-voltage   | $V_{\rm DD} \ [V]$        | 12  | 12    | 5    | 12   |

| Failure-voltage | $V_{\rm DS} \ [V]$        | 350 | 400   | 450  | 225  |

| Failure-time    | $t_{ m SC} \; [\mu s]$    | 20  | 40    | >250 | -    |

illustrated in TABLE I, with their respective achievements of SC capability. In the range of bias currents  $I_{\rm G}$  (obtained from  $(V_{DD} - V_{GS}) / R_G$ , an insignificant nominal reduction of on-state performance is predicted. Therefore, condition A corresponds to a high and B to a low value within this range, in order to investigate transferability on the SC performance and the capability respectively. To investigate the implication of  $V_{\rm DD}$ , the characteristics of condition C, which exhibits a lower value, are compared to condition B. In order to keep a comparable low bias current  $I_G$  condition, the value of  $R_{\rm G}$  is reduced. Due to the GBD (as extensively explained in chapter VI) a decrease of  $V_{GS}$ , correlated to an increase of  $V_{\rm DS}$ , can be observed. For comparability of p- and insulatedgate devices, the aim of condition D is to disregard the GBD. Therefore, in all terms of operation, an adjustment of  $R_{\rm G}$  is necessary to ensure a constant operation point.

### IV. VOLTAGE TO FAILURE

The procedure of investigating the voltage restricted SC capability (see TABLE III) involves a retain of the minimum required SC duration and a stepwise increase of the voltage

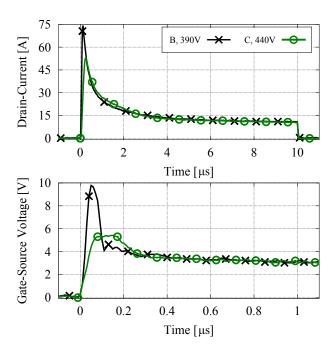

Fig. 3: Drain-current vs. time (top), gate-source voltage vs. time - zoom (bottom). Experimental results of maximum achieved voltage capability, by comparing conditions B and C.

$V_{\rm DS}$ , until a failure occurs.

Reaching the voltage restriction leads, in all conditions, to a device destruction within a few hundred nanoseconds. The device withstands the required SC duration for voltages  $V_{\rm DS}$  below the failure-voltage, therefore a significant thermal related failure can be neglected. Condition A withstands voltages until  $V_{\rm DS} = 340~V$ , whereas with condition B  $V_{\rm DS} = 390~V$  and with C up to  $V_{\rm DS} = 440~V$  is achieved. The earlier restriction of condition A in comparison to B, can be referred to the gate-current and is further detailed in chapter V. The current  $I_{\rm D}$  and the corresponding  $V_{\rm GS}$  waveforms for conditions B and C are depicted in Fig. 3. Therefore, the major difference is related to the initial value of the current  $I_{\rm D,peak}$ , see Fig. 3 (bottom). The carrier density affects the magnitude of the electrical field, which leads to an electrical breakdown in the structure for an exceedance of a critical value.

Furthermore, the range of voltage withstand capability, defined as ratio of failure- and the nominal breakdown voltage, diverse from approximately 60% up to 75% regarding the condition variation.

## V. TIME TO FAILURE

The investigation of the SC duration capability (see TA-BLE III) is similar to the procedure for the voltage restriction. Therefore, the minimum required voltage  $V_{\text{DS}}$  is kept constant and the time  $t_{\text{SC}}$  is stepwise increased, until a failure occurs.

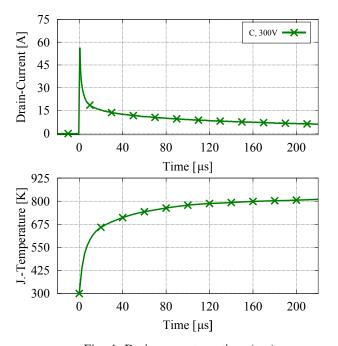

For condition C, an SC duration related restriction has not been observed. The waveform of the current  $I_D$  is depicted in Fig. 4 (top), together with an estimation of the junctiontemperature in Fig. 4 (bottom). The temperature is determined with a numerical 3D temperature simulator which is presented

Fig. 4: Drain-current vs. time (top), junction-temperature vs. time (bottom). Extract of the experimental achieved SC duration capability of condition C.

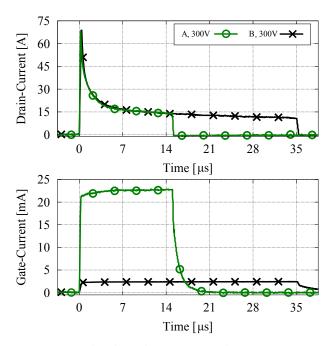

Fig. 5: Drain-current vs. time (top), gate-current vs. time (bottom). Experimental results of maximum achieved SC duration capability, by comparing conditions A and B.

in [4]. The temperature settles for  $t_{\rm SC} \ge 160 \ \mu s$ . An abrupt thermal related failure for higher durations is not expected, based on the results of this investigation respectively the performed operation condition.

For conditions A and B, a clear limitation of the SC duration is observed. The comparison with condition C further emphasizes that the failure is mainly related to the initial value of the current  $I_{D,peak}$  (see chapter IV). Considering equal peak values  $I_{D,peak}$ , in terms of condition A and B, an underlying limitation can be observed. The current  $I_D$  waveform, for these two conditions within the last measurement before device destruction are depicted in Fig. 5 (top). Whereas the progression of  $I_D$  is identical, the main difference can be observed at the gate-bias current  $I_G$ . The respective waveforms of  $I_G$  are depicted in Fig. 5 (bottom). The value of  $I_G$  for condition A is one order of magnitude higher than in B. The injection of holes into the gate increases with the amount of the current  $I_G$ . Therefore, an assumption of hole accumulation under the gate [2] can be made.

### VI. GATE-BIAS DEPENDENCE

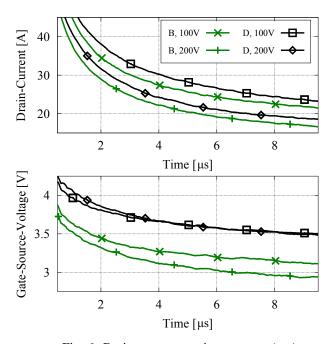

The SC behaviour of conditions B and D, for two different  $V_{\rm DS}$ , shows the significant characteristics of the GBD. Therefore, depicted in Fig. 6 (top), the zoom into the SC saturation region of  $I_{\rm D}$  the corresponding  $V_{\rm GS}$  (bottom). Comparing the current saturation values  $I_{\rm D,sat}$  at a specific voltage (e.g  $V_{\rm DS} = 100 V$ ), indicates a significant lowering for condition B. This characteristic are further observed for the value of the saturation voltage  $V_{\rm GS,sat}$ . Furthermore, for both conditions an approximately identical lowering of the current saturation values  $I_{\rm D,sat}$ , between the two different voltages (e.g.  $V_{\rm DS} = 100 V$  to  $V_{\rm DS} = 200 V$ ), occurs. According to the specific aim of condition D (see chapter III) a constant value of  $V_{\rm GS,sat}$  is achieved, whereas a  $V_{\rm DS}$  dependency occurs in case of condition B. However, the change of  $I_{\rm D,sat}$ , for a constant bias at condition D, also refers to a thermal mobility degeneration due to excessive power dissipation [3], as discussed in chapter III. Consequently, the further difference of the saturation values between conditions B with D relates to the impact of the GBD.

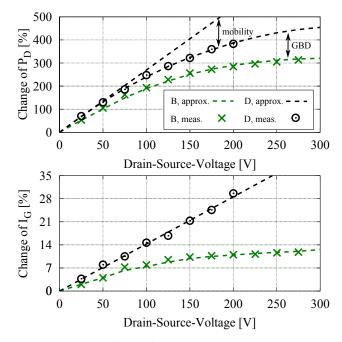

For an ideally constant current  $I_{\rm D}$ , the power dissipation behaves linear within the device, at an increase of voltage  $V_{DS}$ . According to the thermal mobility degradation a non-uniform power dissipation occurs. Due to the GBD, a further gain of non-uniformity, for the operation of the p-gate HEMT, can be observed. The extent is illustrated as the percentage change of the dissipated power  $P_D$  in Fig. 7 (top) and current  $I_G$  (bottom), as function of  $V_{\rm DS}$  within the minimum required range. Therefore, the percentage change is defined as the ratio of saturation values (at  $t_3$ , referring to the definition in chapter III) and the respective low voltage SC value. The forced increase of  $I_{G}$  in condition D, in order to achieve a constant operation point, leads to a voltage related failure at  $V_{\text{DS}} = 225 V$ . Therefore, measurements of higher  $V_{\rm DS}$  values could not be achieved. Therefore, the existence of the early failure confirms the observations obtained in chapter V. However, the GBD manifests itself in an unintended increase of  $I_{G}$  approximately  $(4\% \cdot I_G) / (100 V)$  for  $V_{\rm DS} \ge 125 V$ . Furthermore, the pgate HEMT provides, for increasing values of the drain-source voltage, a respective self-contained lowering of performancerelated temperature gain.

Fig. 6: Drain-current vs. time - zoom (top), gate-source voltage vs. time - zoom (bottom). Experimental results, illustrating the significant behaviour of the gate-bias dependence, by comparing conditions B and D.

Fig. 7: Power dissipation vs. drain-source voltage (top), gate-current vs. drain-source voltage (bottom).

Experimental results, illustrating the impact of the gate-bias dependence, by comparing conditions B and D. Therefore, the change is defined as e.g.:

$P_{\text{D,sat}}(V_{\text{DS}}) / P_{\text{D,sat}}(V_{\text{DS}} \le 3 V) \cdot 100\%$

## CONCLUSION

This paper has shown that the short-circuit withstand capability of p-Gate GaN HEMTs is mainly limited by the initial drain-current peak and the value of the gate-current. Both factors are strongly dependent on the design of the gate-drive circuit: optimised design can yield voltage robustness up to 75%, with very long pulse widths for lower values. The observed gate-bias dependence exhibits a self-protecting decrease of the current and power dissipation level during the pulse. Due to this, higher short-circuit capability is achieved if the drain-current peak and gate-current value is kept low, for increased voltages.

#### REFERENCES

- E.A. Jones, F. Wang, and B. Ozpineci, "Application-Based Review of GaN HFETs," 2014 IEEE Workshop on Wide Bandgap Power Devices and Applications, Knoxville, TN, 2014, pp. 24-29.

- [2] X. Huang, D.Y. Lee, V. Bondarenko, A. Barker, D.C. Sheridan, A.Q. Huang and B.J. Baliga, "Experimental Study of 650V AlGaN/GaN HEMT Short-Circuit Safe-Operating Area (SCSOA)," 2014 IEEE 26th International Symposium on Power Semiconductor Devices & IC's (ISPSD), Waikoloa, HI, 2014, pp. 273-276.

- [3] T.T. Mnatsakanov, M.E. Levinshtein, L.I. Pomortseva, S.N. Yurkov, G.S. Simin, and M.A. Kahn, "Carrier mobility model for GaN," *Solid-State Electronics*, 2003, 47, pp. 111-115.

- [4] M. Mocanu, C. Unger, M. Pfost, P. Waltereit, and R. Reiner, "Thermal Stability and Failure Mechanism of Schottky Gate AlGaN/GaN HEMTs", *IEEE Transactions on Electron Devices*, 2017, pp. 848-855.