Power Electronic Autotransformer Based 3×25 kV Network for Power Quality Enhancement In Railway Supply Systems

Tabish Nazir Mir\*†, Member, IEEE and Pietro Tricoli†, Senior Member, IEEE

Abstract—State of the art single-phase AC traction systems are based on a split-phase 2×25kV supply network with multiple regularly spaced auto-transformers. The main drawbacks of this arrangement are the unbalanced currents in the three-phase grid and reactive power flow due to transformers and autotransformers. This paper proposes to solve these issues with a completely new 3×25 kV railway power supply supported by a power electronic autotransformer (PEAT). The PEAT circuit comprises of single-phase back-to-back voltage source converters, connected across different phase pairs of the threephase network. These voltage-source converters balance the three-phase grid current for all traction load conditions, ensuring grid compliant power quality performance. Over and above that, the PEAT system enables reactive power control and ensure unity power factor at the point of connection. Besides detailing the control algorithm for the PEAT system, this paper also discusses various design aspects and optimal positioning of the PEAT unit along the railway line. The efficacy of the PEAT topology is illustrated through extensive simulations carried out in Matlab/Simulink environment. These are further validated via real time hardware-in-the-loop (HIL) results obtained from a Typhoon HIL 404 device together with a C2000 microcontroller based interface card.

Index Terms—AC railway systems, power quality, power electronic autotransformer, railway electrification, grid current balancing, hardware-in-the-loop (HIL) systems

## I. Introduction

S THE world battles climate change, concerted efforts A are being made towards sustainability through transport decarbonisation. This has led to landmark improvements in technology areas such as more-electric aircraft, electric railways and electric vehicles. Electric railways have particularly emerged as the most promising means of sustainable transport due to their bulk transit capability and relatively matured technology status. However, railway electrification is recognized to pose significant power quality challenges to the three-phase  $(3-\phi)$  AC grid, with current imbalance being the paramount cause of concern in all AC rail networks [1]. Railway power networks and utilities often enforce specific requirements on parameters such as power quality, percentage unbalance, and voltage regulation. Typically, high speed AC rails span power levels of 2-5 MW per train. Connection to the high voltage grid at such power levels requires stringent power quality criteria to be met, which are often dictated by the transmission code (or the grid code). Moreover, railway networks are also expected to meet voltage regulation criteria, with a permissible

voltage range of 19 kV to 27.5 kV [2]. Maintaining this voltage profile at given power levels, often restricts the length of each feeder to about 40-60 km, demanding separate feeding stations and hence neutral sections (or circuit breaking arrangements) at regular intervals. Commonly, railway sub-station power supplies are tapped from phase pairs of the 3- $\phi$  132 kV grid, and stepped down to  $\pm$  25 kV supply through split-phase step down transformers [2]. In such systems, trains are connected between the overhead line at +25 kV and running rails at 0 V, while a negative feeder at -25 kV runs parallel to the rail line. This split-phase arrangement reduces power losses through autotransformers (ATs) that are placed at regular intervals (every 5-8 km) along the line to divert returning currents to the -25 kV negative feeder [3]. Although the 2×25 kV AT based railway power networks are popular worldwide, they cause  $3-\phi$ grid current imbalance, thereby resulting in voltage imbalance at the point of common coupling (PCC). In order to maintain uniform loading, multiple substations tap different phase pairs of the 3- $\phi$  grid with electrically isolated neutral sections between substations. These neutral sections are additional to the ones necessitated between feeding sections. Such a design negatively affects the speed of trains in European systems, as trains are not supplied while crossing the neutral sections, and add complexity to Asian systems as additional heavy-duty circuit breakers are needed to switch the train's power supply from one section to the next. Furthermore, regularly spaced ATs in the network contribute towards unwanted reactive power flow.

Several solutions have been documented to mitigate the power quality issues posed by AT based 2×25 kV railway supply systems [4-8]. In [4], the authors propose the compensation of grid current unbalance through unconventional transformer connections, albeit this is not effective in all load conditions. Some literature also documents the use of static VAR compensators with energy storage elements to compensate for the negative sequence component of grid currents [5]. However, they are prone to resonance problems besides contributing to increased system footprint. More recent and promising advances in railway electrification propose the use of static synchronous compensators (STATCOMs) or co-phase rail power flow controllers (RPFCs) for mitigating power quality problems in traction power supplies [9–13]. Although co-phase RPFC systems offer a fair degree of imbalance compensation and reactive power control, they are known to

1

<sup>\*</sup>Power Electronics and Machines Control Research Group, University of Nottingham, Nottingham, NG7 2GT, U.K.

<sup>&</sup>lt;sup>†</sup>Birmingham Centre for Railway Research and Education, University of Birmingham, Birmingham, B15 2TT, U.K.

employ special transformer arrangements with Scott-T or V-V connections where the two phase outputs are  $90^o$  apart as opposed to classical AT based systems where the phases are split  $180^o$  apart [14]. It is well established that Scott-T/V-V or center-tapped  $1\text{-}\phi$  transformers offer smaller efficiency with a larger size when compared to  $3\text{-}\phi$  transformers. Due to higher conductor efficiency and reduced size,  $3\text{-}\phi$  transformers are preferred unanimously in all high power applications where uniform loading is expected for all three phases.

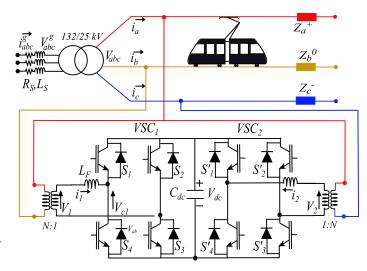

This paper proposes new approach based on a 3×25 kV railway supply system with a power electronic autotransformer (PEAT) for the mitigation of grid current unbalance in railway power supplies. The proposed system uses standard threephase transformers in railway substations instead of Scott or centre-tapped 1- $\phi$  transformers. Utilizing the same three-wire system used by traditional 2×25 kV, the PEAT circuit enables the existing network to operate as a balanced three-phase system even with a 1- $\phi$  train load. As shown in Fig.1, the PEAT topology comprises of back to back 1- $\phi$  voltage source converters (VSCs), connected across different phase pairs of the three-phase railway power supply. While maintaining a constant DC link voltage, the VSCs are controlled to draw balanced 3- $\phi$  grid currents with simultaneous reactive power compensation. The main innovative contributions of the proposed PEAT system are enlisted as,

- The proposed system creates a balanced 3×25 kV railway supply system with 1-φ train loads while using existing 2×25 kV railway electrification conductor infrastructure. Previously documented literature on railway compensators are mostly based on co-phase systems [9] where the existing negative feeder is unutilized.

- Besides compensation of grid current unbalance, the PEAT system offers reactive power and harmonic compensation through appropriate control of back to back VSC units. Although these objective are also achieved in [15], it is at the cost of additional passive requirements and co-phase supply with unused negative feeder.

- Unlike previously reported power converter based compensation solutions that require special Scott/V-V transformer designs [7, 14], the PEAT system can operate with a 3-φ substation transformer that offers benefits of cost, efficiency and easier multiplicity.

- By replacing the split-phase  $2\times25$  kV railway supply by a  $3-\phi$  supply, the PEAT system eliminates swapping of supply phase-pairs and intermittently placed passive auto-transformers. As a result, the proposed system significantly reduces neutral section requirements, thereby, improving the speed profile and lowering circuit breaking requirements in comparison to classical railway supply systems described in [2].

- Finally, the paper details various design and control aspects of the PEAT system. Through performance assessment of unbalance compensation, it further arrives at the optimal location of the PEAT unit, ensuring best performance as the trains travel on the line, which has not been reported for compensators proposed so far [5–12]. The analysis is well supported through simulation results

and evidenced through real time hardware-in-the-loop (HIL) results obtained using Typhoon HIL 404 device with a C2000 micro-controller (F28379D) based interface card.

Fig. 1. Basic structure of the PEAT augmented 3×25 kV railway power supply

# II. DESIGN AND POSITIONING OF POWER ELECTRONIC AUTOTRANSFORMER

This section discusses various design features of the PEAT, specifically component sizing, selection of voltage levels, filter impedances and overall system parameters. Different components of the existing rail network, PEAT system, its ratings and specifications are tabulated in Table-I. The same data has been used in simulation and HIL analysis outlined in the later sections of the paper. The transformer and grid impedance data are derived from [2, 16], conductor impedances are taken from [17], and the design values of different PEAT components are achieved from suitable calculations as discussed in Section II (A). Further ahead, this section outlines different possible installation positions of the PEAT system, and the effect of PEAT positioning on the compensation performance.

#### A. Design of PEAT system

It can be seen from Fig.1, that the PEAT unit connects to the high voltage ( $3\times25~\mathrm{kV}$ ) grid via interfacing transformers, that step-down the 25 kV (L-L) grid voltage to 1800 V on either side of the PEAT unit. The voltage level selection is based on a compromise between corresponding power levels and feasible converter ratings. For the filter parameters given in Table-I, the converter side voltage ( $V_{c1}$ ) and subsequently the minimum DC link voltage ( $V_{dc}$ ) are calculated.

$$V_1^{p.u} = jI_1^{p.u} X_F + V_{c1}^{p.u}$$

(1)

Even though the PEAT unit handles only a fraction of the total power of the traction substation, calculations are made for the worst case scenario assuming the PEAT unit operating at its maximum capacity. The converter input current  $i_1$  is also

TABLE I Design Specifications of  $3\times25$  kV Railway Power Supply

2 V 25 LV Dailway Natwork

| 3×25 kV Railway Network                 |                                   |

|-----------------------------------------|-----------------------------------|

| $3-\phi$ railway transformer            | N = 132  kV/25  kV, 18  MW        |

| Grid impedance $(R_s, L_s)$             | $1\Omega, 32 \text{ mH}$          |

| Power rating of each train unit         | 5 MW                              |

| Impedance of overhead line $(Z_a^+)$    | $0.037~\Omega$ /km, $0.43~m$ H/km |

| Impedance of running rails $(Z_b^-)$    | $0.023~\Omega$ /km, $0.22~m$ H/km |

| Impedance of negative feeder $(Z_c^0)$  | $0.054\Omega$ /km, $0.63$ mH/km   |

| Length of the train line                | 60 km                             |

| Power Electronic Autotransformer (PEAT) |                                   |

| $1-\phi$ interfacing transformers (N:1) | 25000/1800 V                      |

| Filter inductance $(L_F)$               | 0.35  mH                          |

| Nominal DC link voltage                 | 3000 V                            |

| Power rating                            | 5 MW                              |

| DC link capacitor $(C_{dc})$            | $8000 \mu \; { m F}$              |

| VSC switching frequency $(f_{sw})$      | 5 kHz                             |

| Simulation Specifications               |                                   |

| Controller & System Implementation      | Matlab/Simulink                   |

| Sample time                             | $5 \mu s$                         |

| HIL Specifications                      |                                   |

| System Implementation                   | Typhoon HIL                       |

| Sample time (Typhoon HIL)               | $5~\mu s$                         |

| Controller Implementation               | C2000 F28379D                     |

|                                         |                                   |

assumed to be at the same phase as voltage,  $v_1$ . Therefore from (1), the per unit converter input voltage,  $V_{c1}^{p.u}$  is given as,

Sample time (Controller)

$$V_{c1}^{p.u} = 1\angle\theta - (1\angle\theta)(j0.17) = 1.01435\angle(\theta - 9.65)^{\circ}$$

(2)

The choice of filter inductor is a trade-off between the quality of converter (and hence grid) currents, and the minimum DC link voltage ( $V_{dc}$ ). For a modulation index of 0.9, the minimum  $V_{dc}$  is given as,

$$V_{dc} \ge \frac{\sqrt{2} |V_{c1}|}{0.9} \Rightarrow V_{dc} \ge 2868.87 \ V$$

(3)

$50 \mu s$

To ensure grid-compliant current waveforms, the filter inductor has been chosen at 0.17 p.u and the DC link is maintained at 3000 V. Sizing of the DC link capacitor [18] is achieved on the basis of constraints on DC link voltage ripple and the regulation response time,

$$C_{dc} \ge \frac{\mathbf{T} \times \Delta P}{2V_{dc} \times \Delta V_{dc}} \tag{4}$$

Here, the response time of DC voltage regulation loop (T) is chosen to be 5 switching cycles, the maximum variation in power  $(\Delta P)$  is chosen at 5MW, and a 5% allowable variation in DC link voltage is assumed.

$$C_{dc} \ge \frac{0.001 \times 5 \times 10^6}{2 \times 3000 \times 150} \Rightarrow C_{dc} \ge 5555.55 \mu F$$

(5)

A DC link capacitor of  $8000~\mu F$  has been chosen in this work. With the increasing commercial availability of high power IGBT Modules, solid state device requirements of power converters designed at traction power levels as in a PEAT system, can now be met by a range of IGBTs from different manufacturers. These include press pack IGBT mod-

ules from Infineon (P3000ZL45X168, 4500 V, 3000 A) and ABB Stakpak IGBT Modules (5SNA 3000K452300, 4500V, 3000A). However, to lower device ratings or to further increase power levels, interleaved and cascade connections of PEAT converters may also be considered. Since this paper focuses on proof of concept, associated design of passive components, and optimal positioning of PEAT system, back to back 2-level VSIs are considered for the sake of simplicity.

## B. Positioning of PEAT system

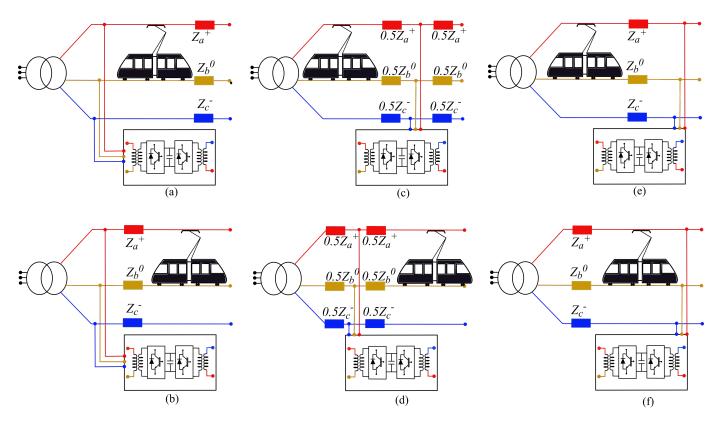

Compensation performance offered by the PEAT unit depends on the position of its installation, and varies with the movement of trains along the feeding section. Typically, only one PEAT unit is required per feeding section. Fig.1 shows the PEAT system connected to the  $3\times25$  kV network next to the traction transformer. However, other installation points are also feasible. For the analysis, three positions of the PEAT unit are considered, i.e PEAT at the start, centre and end of the line. Each PEAT position is studied for compensation performance when the train is at the start and when it is at the end of the feeding section. The resulting six case scenarios are illustrated in Fig.2. Intuitively, the closer the PEAT is installed to the  $1\phi$ train, better is the compensation performance, indicating that a centrally placed PEAT is optimal, as this leads to the lower average distance from the trains. While considering PEAT positioning, it is also important noting that this paper proposes the use of existing conductor infrastructure for establishing a three-phase railway power supply. Therefore, the positive conductor, running rails, and the negative conductor translate to phases a, b, and c, respectively, in the proposed  $3\times25$  kV network. The impedance data per kilometre (km),  $Z_a^+$ ,  $Z_b^0$ and  $Z_c^-$ , of these conductors [3, 17] are given in Table-I, and positioning analysis is done assuming a total feeding section length of 60 km. Since the three conductor impedances are not identical, they also contribute towards system unbalance particularly for long railway lines, thereby making the decision of PEAT positioning, even more critical. Compensation performance for different PEAT positions is analysed subsequently through simulations in Section IV(A).

# III. CONTROL OF POWER ELECTRONIC AUTOTRANSFORMER

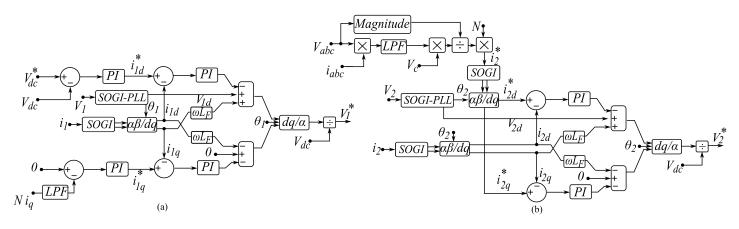

As already mentioned, the PEAT system comprises of two  $1\phi$  VSC units, each of which is controlled independently, such that the PEAT system and the trains, together act as a balanced  $3\phi$  load on the proposed  $3\times25$  kV railway network. One of the voltage source converters, VSC<sub>1</sub> connected across the same phases as the trains, i.e. 'a' and 'b', is designated to regulate the DC link voltage. On the other hand, VSC<sub>2</sub> is controlled to draw current of appropriate magnitude from phase 'c' in phase with the corresponding voltage. In this way, power distribution is achieved between phases to obtain desired balancing. The control of each converter is undertaken in the synchronous reference frame (dq frame), which is made possible by generating quadrature components of  $1\phi$  signals

Fig. 2. Positioning of the PEAT system; (a) Train at start of the line when PEAT is positioned at the start. (b) Train at end of the line when PEAT is positioned at the start. (c) Train at the start when PEAT is positioned at the centre of the line. (d) Train at the end when PEAT is positioned at the centre of the line. (e) Train at start of the line when PEAT is positioned at the end. (f) Train at end of the line when PEAT is positioned at the end.

wherever necessary [19, 20]. The control algorithm is detailed in the following section.

# A. Control of VSC<sub>1</sub>

For the control of VSC<sub>1</sub>, dq reference current commands are first generated, which are converted into a reference voltage command to implement pulse width modulation (PWM). These dq current references are generated for DC link voltage regulation and  $3\phi$  reactive power minimization, respectively. With reference to Fig.1, these are given as,

$$i_{1d}^* = (V_{dc}^* - V_{dc}) \left[ k_{d1}^p + \frac{k_{d1}^i}{s} \right]$$

$$i_{1q}^* = \left[ 0 - (N \times i_q) \left( \frac{1}{0.01s + 1} \right) \right] \left[ k_{q1}^p + \frac{k_{q1}^i}{s} \right]$$

(6)

The transformer secondary voltage,  $V_1$ , is sensed and its quadrature component is generated using a second order generalized integrator (SOGI) [19], which is then used to deduce the phase angle,  $\theta_1$ . Further, the converter input current,  $i_1$ , is measured and its dq components are determined for

Fig. 3. Controller implementation for; (a)  $VSC_1$  (b)  $VSC_2$

comparison with the reference currents generated in (6) to yield the dq reference voltages after appropriate decoupling compensation.

$$v_{1d}^* = \frac{1}{V_{dc}} \left[ v_{1d} - (i_{1d}^* - i_{1d}) \left( k_{d1}^p + \frac{k_{d1}^i}{s} \right) + \omega L_F i_{1q} \right]$$

$$v_{1q}^* = \frac{1}{V_{dc}} \left[ 0 - (i_{1q}^* - i_{1q}) \left( k_{d1}^p + \frac{k_{d1}^i}{s} \right) - \omega L_F i_{1d} \right]$$

$$(7)$$

Finally, the  $1\phi$  reference voltage for PWM implementation in VSC<sub>1</sub> is given as,

$$v_1^* = v_{1d}^* sin(\theta_1) + v_{1q}^* cos(\theta_1)$$

(8)

## B. Control of $VSC_2$

The principle of control for VSC<sub>2</sub> is to complement VSC<sub>1</sub> in maintaining balanced  $3\phi$  sinusoidal grid currents. This is achieved by developing an appropriate grid current reference,  $i_c^*$  for the phase that is not connected to the train load. Subsequently, a  $1\phi$  reference voltage command for VSC<sub>2</sub> is generated, and the converter is controlled to draw current  $i_c$  from the grid that follows the command current,  $i_c^*$ . This reference grid current,  $i_c^*$  for balanced  $3\phi$  operation, is determined from the instantaneous power drawn from the grid, and aligned with phase voltage,  $v_c$  for UPF operation.

$$i_c^* = \left[ \left( \frac{v_a \cdot i_a + v_b \cdot i_b + v_c \cdot i_c}{0.01s + 1} \right) \left( \frac{v_c}{v_a^2 + v_b^2 + v_c^2} \right) \right]$$

(9)

Since phase 'c' of the  $3\times25$  kV network is not connected to the grid, it is solely controlled by VSC<sub>2</sub>. Therefore,  $i_c^*$  directly translates to current reference,  $i_2^*$  for VSC<sub>2</sub>.

$$i_2^* = N \times i_c^* \tag{10}$$

Again, using a SOGI implementation, the stationary components and subsequently synchronous components of  $i_2^*$  are determined using the phase angle,  $\theta_2$  obtained from voltage,  $V_2$ . The dq current commands are converted to voltage commands as follows,

$$v_{2d}^* = \frac{1}{V_{dc}} \left[ v_{2d} - (i_{2d}^* - i_{2d}) \left( k_{2d}^p + \frac{k_{2d}^i}{s} \right) + \omega L_F i_{2q} \right]$$

$$v_{2q}^* = \frac{1}{V_{dc}} \left[ 0 - (i_{2q}^* - i_{2q}) \left( k_{2q}^p + \frac{k_{2q}^i}{s} \right) - \omega L_F i_{2d} \right]$$

(11)

Finally, the  $1\phi$  reference voltage for PWM implementation in VSC $_2$  is given as,

$$v_2^* = v_{2d}^* \sin(\theta_2) + v_{2d}^* \cos(\theta_2) \tag{12}$$

Therefore, each converter of the PEAT unit is controlled individually, such that an overall balanced  $3\phi$  system with reactive power compensation is achieved. Block diagrammatic representations of the controller implementations for VSC<sub>1</sub> and VSC<sub>2</sub> are illustrated in Fig.3(a) and 3(b), respectively.

#### IV. RESULTS AND ANALYSIS

In order to validate the performance of the PEAT system and the proposed 3×25 kV railway power network, detailed simulation and real-time hardware-in-loop (HIL) results are presented. Computer simulations are carried out in Matlab/Simulink environment, which are further corroborated through HIL testing using Typhoon HIL 404 device.

#### A. Simulation Results

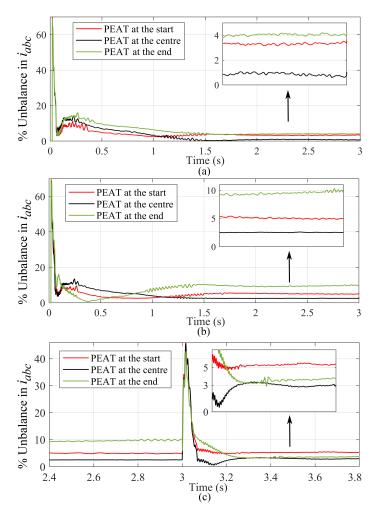

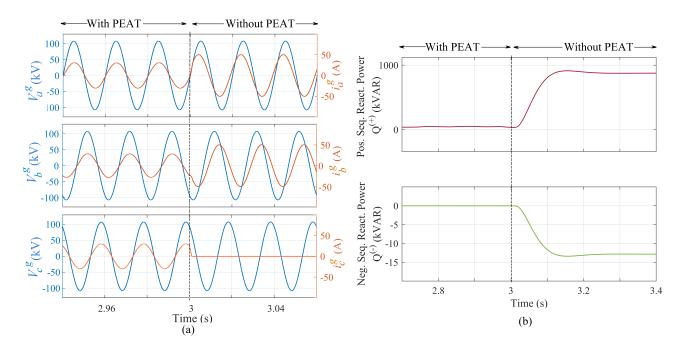

The effect of PEAT positioning on system balancing performance for different case scenarios, is illustrated in Fig.4. It represents the percentage unbalance (i.e ratio of negative to positive sequence components) in  $3\phi$  grid currents for different PEAT installation points (start, centre and end) along the feeding section, when the train is at the start of the line (Fig.4(a)) and at the end of the line (Fig.4(b)). Fig.4(c) illustrates the dynamic compensation performance of the PEAT unit at different installation points, when a second train load is introduced at the start of the line, with an existing train load at the end of the line. The percentage unbalance of each case is

Fig. 4. Percentage unbalance in  $3\phi$  grid currents for different PEAT installation points; (a) when train is at the start of the line. (b) when train is at the end of the line. (c) when a second train is introduced at the start of the line, with an existing train at the end of the line.

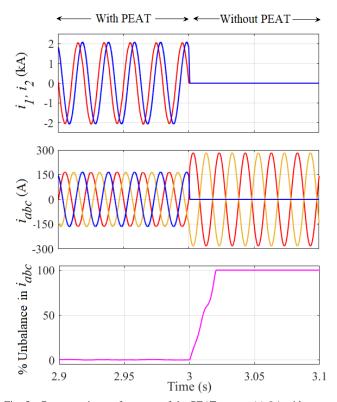

Fig. 5. Compensation performance of the PEAT system (a)  $3\phi$  grid currents and their percentage unbalance with and without the PEAT in place (b)  $3\phi$  grid voltage and their percentage unbalance with and without the PEAT in place

Fig. 6. Compensation performance of the PEAT system (a)  $3\phi$  grid currents and their percentage unbalance with and without the PEAT in place (b)  $3\phi$  grid voltage and their percentage unbalance with and without the PEAT in place

demonstrated with respect to time. Data in Figs.4(a) & 4(b) is captured as soon as the PEAT unit is made operational at t=0, until steady state unbalance compensation is achieved. Fig.4(c) is a time continuation of Fig.4(b), where initial compensation steady state has been achieved for train at the end of the line and another train is then introduced at the start of the line at t=3 s. Each figure has a zoomed in version of the steady state compensation performance to help identify the most optimum location of the PEAT unit. Quite evidently, the most optimum location for PEAT positioning is at the centre of the line, irrespective of the position of the trains. Even instinctively, a centrally placed PEAT is optimal, as this leads to the lowest average distance of the PEAT unit from the trains in transit.

Figs. 5 and 6 show the simulation results for compensation performance of the PEAT system, in terms of grid current and voltage parameters. Fig.5 sequentially shows the compensating converter currents  $(i_1, i_2)$ , the  $3\phi$  grid currents  $(i_{abc})$  and the percentage unbalance in  $i_{abc}$ , with the PEAT in place and also when the PEAT system is disconnected at t= 3 seconds. Quite evidently, as soon as PEAT is disconnected, the grid current unbalance rises to 100% due to the 1- $\phi$  train load, which is otherwise fully compensated by the PEAT unit to appear as a balanced 3- $\phi$  load on the network.

In  $1-\phi$  railway systems, grid current unbalance may also reflect on the voltage profile of the grid, and may cause violation of the transmission grid code, especially when multiple trains are plying on the route. By compensating for grid current unbalance, the PEAT system also enhances the grid voltage balancing performance. This is well illustrated in Fig.6, which shows the  $3\phi$  grid voltages and their percentage unbalance with and without the PEAT in situ. It is seen that in the absence of PEAT compensation, the grid voltage unbalance exceeds 1% which violates the transmission grid code of most countries. Since, the voltage unbalance is not as pronounced as current unbalance, a vertically zoomed section of grid voltages is also shown in Fig.6 to clearly show the balancing effect of PEAT.

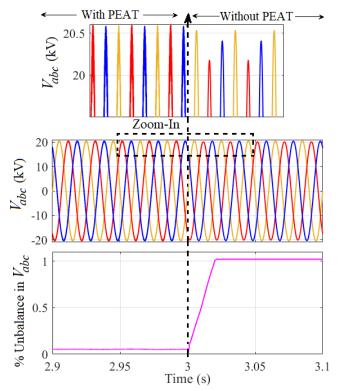

Finally, to illustrate reactive power compensation offered by the PEAT system, Fig.7 shows the individual phase voltage and current profiles, and the reactive power flow for the  $3\phi$ , 132 kV grid. As seen in Fig.7(a) each phase current is maintained in phase with the corresponding voltage when the PEAT system is in place. However, with the PEAT disconnected, the system behaves like the traditional  $2 \times 25$  kV suppy with singlephasing effect on the  $3\phi$ , 132 kV grid. Not only does this cause unbalance in grid currents, but the currents also deviate in phase with respect to corresponding voltages. It is imperative to note, that reactive power flow in an unbalanced system, manifests as positive sequence  $(Q^{(+)})$  as well as negative sequence components  $(Q^{(-)})$ . From Fig.7(b), it can be seen that the proposed PEAT compensated system has nearly zero reactive power flow both in terms of  $Q^{(+)}$  and  $Q^{(-)}$ . However, with the PEAT disconnected, the system loses its reactive power compensation capabilities. For the conventional uncompensated system, substantial reactive power flow,  $Q^{(+)}$  is observed to be associated with reactive elements in the system, such as reactance of the feeding sections and transformers. Moreover, due to the single-phasing effect of conventional systems on the  $3\phi$  grid, negative sequence reactive power flow,

Fig. 7. Role of PEAT in reactive power compensation; (a) Individual phase voltages and corresponding phase currents with and without PEAT in place. (b) Positive and negative sequence reactive power flow with and without PEAT in place.

## $Q^{(-)}$ is also observed in the absence of PEAT.

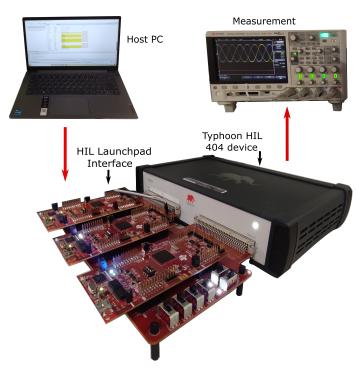

Fig. 8. Hardware-in-loop test bench with Typhoon HIL 404 device as real-time simulator and FR28379D based controller

## B. Hardware-In-Loop Testing

Hardware-in-loop (HIL) testing is conducted using Typhoon HIL 404 device to experimentally verify the validity of the controller. The  $3\times25$  kV railway power supply and the PEAT system is implemented in Typhoon HIL Control Centre,

whereas the control algorithm is developed using C2000 micro-controller ( $\mu C$ ) from Texas Instruments. Each VSC is operated through a dedicated  $\mu C$  launchpad F28379D, that is further integrated to the Typhoon HIL 404 device through the Typhoon HIL TI microGrid launchpad interface. HIL results are recorded on a Mixed Signal Oscilloscope (MSOX2024A Keysight), and analysis is conducted in real-time using the Typhoon platform. The implementation test bench is illustrated in Fig.8.

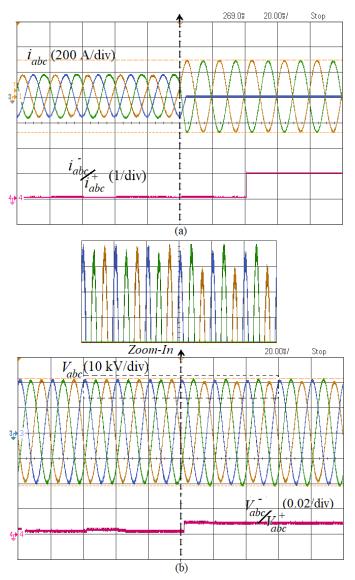

HIL test results for steady state compensation performance of the PEAT system are illustrated in Fig.9. The  $3\phi$  grid currents and the current unbalance, with and without the PEAT system is shown in Fig.9(a). These are seen to corroborate with the simulation results seen in Fig.5. Furthermore, the effect of PEAT system in complying with the transmission grid code, is illustrated through  $3\phi$  grid voltages and voltage unbalance, as shown in Fig.9(b). The figure also shows a zoomed in version of grid voltages to clearly demonstrate voltage unbalance upon disconnection of the PEAT system. Again HIL validation (Fig.9(b)) is in close agreement with simulation results shown in Fig.6.

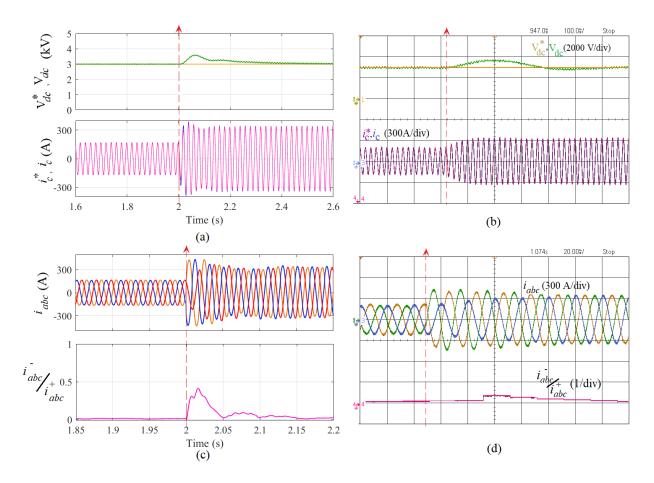

In order to substantiate validation for the proposed system and its control, a fair comparison of simulation and HIL performance has been drawn on the basis of dynamic performance and power quality, in Figs. 10 & 11 respectively. Simulation and HIL test results for dynamic performance of the PEAT system during a change of train load is shown in Fig.10. Fig.10 (a) & (b) respectively show the simulation and HIL based tracking performance of each VSC when a second train is added on the line. As the train load is increased, VSC<sub>1</sub> enables the regulation of the DC link voltage to commanded value of 3 kV. At the same time, the reference current of phase 'c',  $i_c^*$  also steps up to match the increased load

Fig. 9. HIL test results for steady state compensation performance of the PEAT system (a)  $3\phi$  grid currents and their percentage unbalance with and without the PEAT in place (b)  $3\phi$  grid voltages and their percentage unbalance with and without the PEAT in place

demand, and  $VSC_2$  ensures that phase current,  $i_c$  follows the change in command. The response time for DC link voltage regulation is around 10 cycles in simulation and 15 cycles in HIL. The relatively slower response time in Fig.10(b) is attributed to the restriction in sampling rate of the control algorithm as implemented in the C2000 micro-controller interfaced with the HIL system. The grid side impact of the PEAT system during load dynamic performance is depicted as a comparison of simulation and HIL results in Figs.10(c) & (d), respectively. These show the  $3\phi$  grid currents and their percentage unbalance during load dynamics as a second train is introduced into the network. It can be noticed that the new steady-state conditions are achieved after approximately 2-3 cycles in simulation and 4-5 cycles in HIL. For both simulation and HIL results, steady state response is marginally delayed due to the use of second order generalized integrator

(SOGI) in the calculation of the quadrature component of the current, which is inevitable in single-phase converters. It is evident from Fig.10 that simulation and HIL results closely corroborate except for mild inevitable deviations in response time that are attributed to the relatively slower controller rate in HIL test analysis.

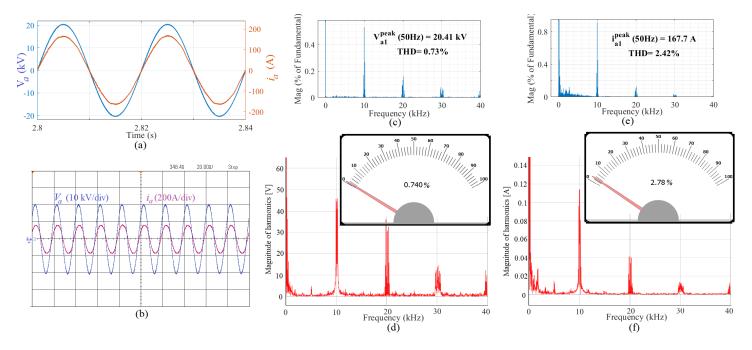

Finally, a comparative analysis of simulation and HIL based power quality performance for the proposed 3×25 kV PEAT supported railway supply is shown in Fig.11. Simulation results for phase voltage of the network and corresponding grid current at near unity power factor is shown in Fig.11 (a), and the corresponding HIL waveforms are seen to corroborate in Fig.11(b). Figs.11(c) & (d) respectively show the simulation and HIL results for harmonic spectra of grid voltage. Figs.11 (e) & (f) respectively show the simulation and HIL results for harmonic spectra of grid current. For harmonic analysis in simulation, the fast fourier transform (FFT) tool of Matlab is used, while the HIL SCADA tool of Typhoon HIL control center is used for harmonic analysis in the HIL domain. Due to the use of unipolar pulse width modulation technique, harmonics in the current spectrum appear at even multiples of the switching frequency. This is also reflected in the harmonic spectrum of voltage at the point of common coupling. From the power quality analysis of Fig.11, simulation and HIL results are clearly seen to be equivalent, with power quality performance conforming to IEEE Std 519.

## V. Conclusion

On the basis of extensive analysis, simulation and HIL test results presented in this paper, it is deduced that a  $3\times25$  kV railway power supply augmented with a power electronics auto-transformer (PEAT), is a powerful alternative to existing railway power systems. The design procedure, positioning and control of the PEAT system has been outlined in this paper. The efficacy of the proposed system is verified through simulation and HIL test results, which are seen to corroborate with each other.

The PEAT system offers significant power quality improvement in terms of unbalance compensation, reactive power control, and grid compliant current waveforms, while using the existing conductor infrastructure. Adding to its advantages, the proposed system uses three-phase transformers in the railway substation instead of specially wound Scott-T or V-V transformers, the latter being inefficient and uneconomical for mass production. An adequately rated PEAT system offers compensation for the entire train line, thus circumventing the use of regularly spaced passive auto-transformers. Furthermore, due to compensation offered by the PEAT unit, the balanced three-phase railway system has an innate ability to operate without swapping of phase pairs, hence reducing neutral sections and circuit breaker requirements. To further remove neutral sections at the end of feeding sections, bilateral railway supplies can be explored with the PEAT system, without any expected deviations in its compensation performance. Being a power converter based active solution, the PEAT system is expected to incur more capital costs and installation complexity than traditional  $2 \times 25$  kV supply systems.

Fig. 10. Comparative analysis of simulation and HIL tests for dynamic performance during change in train load; (a) Simulation results for tracking performance of DC link voltage  $(VSC_1)$  and grid current,  $i_c$   $(VSC_2)$  (b) HIL results for tracking performance of DC link voltage  $(VSC_1)$  and grid current,  $i_c$   $(VSC_2)$  (c) Simulation results for overall unbalance compensation of the PEAT system during load change (d) HIL results for overall unbalance compensation of the PEAT system during load change.

Fig. 11. Comparative analysis of simulation and HIL tests for power quality performance of the proposed system (a) Simulation results for phase voltage and corresponding grid current at UPF (b) HIL results for phase voltage and corresponding grid current at UPF (c) Simulation based harmonic analysis of phase voltage (d) HIL based harmonic analysis of phase voltage (e) Simulation based harmonic analysis of grid current. (f) HIL based harmonic analysis of grid current

Again, in terms of reliability, traditional transformer based passive systems are expected to fare better than the proposed active solution. However, due to the wide array of benefits offered by PEAT over conventional supply systems, coupled with projected improvement in power converter reliability and reduction of semi-conductor costs in the future, the PEAT is a promising technology for long term investment. Another impediment in this technology could be limitations on the design of VSI based PEAT systems at higher power levels. This could be mitigated through topological modifications of the PEAT using interleaved and cascade connections, which encompasses future scope of this work.

#### REFERENCES

- [1] S. M. Mousavi Gazafrudi, A. Tabakhpour Langerudy, E. F. Fuchs, and K. Al-Haddad, "Power Quality Issues in Railway Electrification: A Comprehensive Perspective," *IEEE Transactions on Industrial Electronics*, vol. 62, no. 5, pp. 3081–3090, May 2015.

- [2] R. D. White, "Ac 25kv 50 hz electrification supply design," in 5th IET Professional Development Course on Railway Electrification Infrastructure and Systems (REIS 2011), 2011, pp. 92–130.

- [3] B. Mohamed, P. Arboleya, I. El-Sayed, and C. González-Morán, "High-Speed 2 × 25 kV Traction System Model and Solver for Extensive Network Simulations," *IEEE Transactions on Power Systems*, vol. 34, no. 5, pp. 3837–3847, Sep. 2019.

- [4] G. Firat, G. Yang, and H. A. H. Al-Ali, "A comparative study of different transformer connections for railway power supply-mitigation of voltage unbalance," in 10th International Conference on Advances in Power System Control, Operation & Management (APSCOM 2015), Nov. 2015, pp. 1–6.

- [5] Z. Guiping, C. Jianye, and L. Xiaoyu, "Compensation for the negative-sequence currents of electric railway based on svc," in 2008 3rd IEEE Conference on Industrial Electronics and Applications, 2008, pp. 1958–1963.

- [6] Z. Sun, X. Jiang, D. Zhu, and G. Zhang, "A novel active power quality compensator topology for electrified railway," *IEEE Transactions on Power Electronics*, vol. 19, no. 4, pp. 1036–1042, Jul. 2004.

- [7] A. Luo, C. Wu, J. Shen, Z. Shuai, and F. Ma, "Railway Static Power Conditioners for High-speed Train Traction Power Supply Systems Using Three-phase V/V Transformers," *IEEE Transactions on Power Electronics*, vol. 26, no. 10, pp. 2844–2856, Oct. 2011.

- [8] N. Y. Dai, K.-W. Lao, and C.-S. Lam, "Hybrid Railway Power Conditioner With Partial Compensation for Converter Rating Reduction," *IEEE Transactions on Industry Applications*, vol. 51, no. 5, pp. 4130–4138, Sep. 2015.

- [9] L. Liu, N. Dai, K. W. Lao, and W. Hua, "A Co-Phase Traction Power Supply System Based on Asymmetric Three-Leg Hybrid Power Quality Conditioner," *IEEE Transactions on Vehicular Technology*, vol. 69, no. 12, pp. 14645–14656, Dec. 2020.

- [10] C. Wu, A. Luo, J. Shen, F. J. Ma, and S. Peng, "A Negative Sequence Compensation Method Based on a Two-Phase Three-Wire Converter for a High-Speed Railway Traction Power Supply System," *IEEE Transactions on Power Electronics*, vol. 27, no. 2, pp. 706–717, Feb. 2012.

- [11] M. Zare, A. Y. Varjani, S. Mohammad Dehghan, and S. Kavehei, "Power Quality Compensation and Power Flow Control in AC Railway Traction Power Systems," in 2019 10th International Power Electronics, Drive Systems and Technologies Conference (PEDSTC), Feb. 2019, pp. 426– 432.

- [12] Z. Shu, S. Xie, and Q. Li, "Single-Phase Back-To-Back Converter for Active Power Balancing, Reactive Power Compensation, and Harmonic Filtering in Traction Power System," *IEEE Transactions on Power Electronics*, vol. 26, no. 2, pp. 334–343, Feb. 2011.

- [13] M. Tanta, V. Monteiro, B. Exposto, J. G. Pinto, A. P. Martins, A. S. Carvalho, A. A. N. Meléndez, and J. L. Afonso, "Simplified rail power conditioner based on a half-bridge indirect AC/DC/AC Modular Multilevel Converter and a V/V power transformer," in *IECON 2017 43rd Annual Conference of the IEEE Industrial Electronics Society*, Oct. 2017, pp. 6431–6436.

- [14] F. Ma, A. Luo, X. Xu, H. Xiao, C. Wu, and W. Wang, "A Simplified Power Conditioner Based on Half-Bridge Converter for High-Speed Railway System," *IEEE Transactions on Industrial Electronics*, vol. 60, no. 2, pp. 728–738, Feb. 2013.

- [15] K.-W. Lao, M.-C. Wong, N. Dai, C.-K. Wong, and C.-S. Lam, "A systematic approach to hybrid railway power conditioner design with harmonic compensation for high-speed railway," *IEEE Transactions on Industrial Electronics*, vol. 62, no. 2, pp. 930–942, 2015.

- [16] A. Y. Zakharov, S. O. Gorkavenko, and V. V. Korolev, "Features of the calculation and simulation of a transformer for a substation," in 2019 IEEE Conference of Russian Young Researchers in Electrical and Electronic Engineering (EIConRus), 2019, pp. 744–746.

- [17] A. Mariscotti, P. Pozzobon, and M. Vanti, "Simplified Modeling of 2 x 25 kV AT Railway System for the Solution of Low Frequency and Large-Scale Problems," *IEEE Transactions on Power Delivery*, vol. 22, no. 1, pp. 296–301, Jan. 2007.

- [18] P. Alemi, Y.-C. Jeung, and D.-C. Lee, "DC-Link Capacitance Minimization in T-Type Three-Level AC/DC/AC PWM Converters," *IEEE Transactions on Industrial Electronics*, vol. 62, no. 3, pp. 1382–1391, Mar. 2015.

- [19] F. Rodriguez, E. Bueno, M. Aredes, L. Rolim, F. Neves, and M. Cavalcanti, "Discrete-time implementation of second order generalized integrators for grid converters," in 2008 34th Annual Conference of IEEE Industrial Electronics, 2008, pp. 176–181.

- [20] N. Ikken, A. Bouknadel, A. Haddou, N.-E. Tariba, H. El omari, and H. El omari, "Pll synchronization method based on second-order generalized integrator for single phase grid connected inverters systems during grid abnormalities," in 2019 International Conference on Wireless Technologies, Embedded and Intelligent Systems (WITS), 2019, pp. 1–5.

Tabish Nazir Mir received B.Tech in electrical engineering from National Insitute of Technology, Srinagar, India in 2014. She later graduated from the Indian Institute of Technology (IIT) Delhi with a PhD in power electronics and electric drives in 2020. From 2020 to 2021, she was Assistant Professor at the National Institute of Technology Srinagar, India. From 2021 to 2022, she was a research fellow with the Birmingham Centre for Railway Research and Education (BCRRE) at the University of Birmingham, where she is now an honorary research fellow.

Thereafter, she joined as research associate at the Dyson Future Power Systems Lab at Newcastle University, where she worked on high frequency power electronics for motor drive applications. In March 2023, she joined the Power Electronics and Machines Control Research Group at the University of Nottingham as Assistant Professor. Her research interests include design, modulation and control of power converters, matrix converter fed motor drives, sensor-less control of AC motors, wide band gap power converters, power electronics for electric mobility and power quality.

Pietro Tricoli was born in Naples, Italy, in 1978. He received the M.S. (cum laude) and Ph.D. degrees in electrical engineering from the University of Naples Federico II, Naples, in 2002 and 2005, respectively. He was a Visiting Scholar with the Department of Electrical and Computer Engineering, University of Wisconsin-Madison, Madison, WI, USA, in 2005. In 2006, he was also a Visiting Scholar with the Department of Electrical and Electronic Engineering, Nagasaki University, Nagasaki, Japan. In 2023, he was Visiting Scientist with the Department of

Engineering and Architecture, University of Trieste, Italy. From 2006 to 2011, he was a Post-Doctoral Research Fellow with the Department of Electrical Engineering, University of Naples Federico II. In 2011, he moved to the Department of Electronic, Electrical, and Systems Engineering, University of Birmingham, Birmingham, U.K., as a Lecturer. He was promoted to Senior Lecturer in 2017, Reader in 2021 and Professor in Power Electronics Systems in 2023. He has authored more than 100 scientific papers published in international journals and conference proceedings. His research interests include storage devices for road electric vehicles, railways, and rapid transit systems, wind and photovoltaic generation, railway and marine electrification systems, and modeling and control of multilevel converters. Dr. Tricoli is a member of the IEEE Industrial Electronics Society and the Energy Institute. He is the Web and Publication Chair of the International Conference on Clean Electrical Power. He is also the Deputy Editor-in-Chief of the IET Journal Renewable Power Generation. He is a Registered Professional Engineer in Italy.