# On the 3C-SiC/SiO<sub>2</sub> n-MOS interface and the creation of a calibrated model for the Electrons' Inversion Layer Mobility covering a wide range of operating temperatures and applied gate voltage

Neophytos Lophitis Faculty of Engineering University of Nottingham Nottingham, UK neo.lophitis@nottingham.ac.uk Anastasios Arvanitopoulos Power and Sensor Systems Infineon Technologies Austria AG Villach, Austria a.e.arvanitopoulos@ieee.org

Philip A. Mawby School of Engineering University of Warwick Coventry, UK p.a.mawby@warwick.ac.uk

Abstract-Cubic (3C-) silicon carbide (SiC) metal oxide semiconductor (MOS) devices have the potential to achieve superior performance and reliability. The effective channel mobility can be significantly higher compared to other SiC polytypes due to the smaller concentration of active SiC/SiO<sub>2</sub> interface traps and the gate leakage current can be smaller than other SiC polytypes and silicon (Si) because of the more favourable conduction band offset between 3C-SiC and silicon dioxide (SiO<sub>2</sub>). This work examines the 3C-SiC/SiO<sub>2</sub> n-MOS interface and makes use of three independent sets of experimental data to derive and validate a comprehensive model of the inversion layer mobility in 3C-SiC n-MOS structures. The model derived in this work can be used by technology computer aided design (TCAD) tools and can predict the channel mobility with reasonable accuracy for gate voltages ranging 0V - 20V, and for temperatures ranging 300K - 473K. The ability to reproduce correctly the physical phenomena affecting the 3C-SiC/SiO<sub>2</sub> n-MOS channel mobility in TCAD through an appropriately parameterised model is imperative for the design and optimization of MOS devices like MOSFETs and IGBTs and the further development of 3C-SiC device technology.

## Keywords— Cubic, Silicon Carbide, 3C-, SiC, channel mobility, Metal Oxide Semiconductor, MOS, TCAD, model

## I. INTRODUCTION

When compared to the more mature hexagonal SiC polytypes (4H-, 6H-), 3C-SiC is a Wide Band Gap (WBG) semiconductor with desirable advantages. The ability to grow 3C-SiC on large area Si wafers makes it a low cost alternative, whereas its isotropic properties [1] combined with a reduced population of active  $3C - SiC/SiO_2$  interface traps ( $D_{it}^{3C-SiC/SiO_2}$ ), allows for high effective channel mobility in MOS devices, with reported values of up to 260 cm<sup>2</sup>/Vs [2]–[5]. Importantly, the conduction band offset of 3C-SiC with SiO<sub>2</sub> is 3.7 eV, which is larger compared to the band offset of Si, 6H- and 4H- SiC with SiO<sub>2</sub> (3.2, 2.95, 2.7 eV respectively [6]). The larger conduction band offset can result in a reduced gate leakage current at any given oxide electric field due to reduced Fowler-Nordheim (F-N) tunnelling mechanism. Consequently, 3C-SiC MOS devices

Mike R. Jennings College of Engineering Swansea University Swansea, UK m.r.jennings@swansea.ac.uk

Marina Antoniou School of Engineering University of Warwick Coventry, UK marina.antoniou@warwick.ac.uk

show a real competitive advantage potential.

Recently, 3C-SiC on silicon (Si) substrates with defects density below  $400 \text{cm}^{-1}$  and a 600V vertical Metal Oxide Semiconductor Field Effect Transistor (MOSFET) with specific on-resistance of 8.2 m $\Omega$ cm<sup>2</sup> were demonstrated [7], [8]. Further, a comprehensive set of physics models for TCAD tools of bulk 3C-SiC [9]–[12] was developed, enabling the numerical and physical study, as well as the optimization of 3C-SiC devices [13]–[18]. In this work we report on the physics and TCAD model of the inversion layer electrons' mobility, with scope to allow for more representative simulations of devices with 3C-SiC/SiO<sub>2</sub> regions [15], [17]. It accounts for the complex contribution of multiple mobility reduction factors. Measurements from 3C-SiC MOSFETs [19]–[21] are utilized for the development and evaluation of the model.

#### II. PHYSICS OF THE $3C - SiC/SiO_2$ Interface

The quality of SiO<sub>2</sub> grown on SiC is comparable to SiO<sub>2</sub> grown on Si [22], [23] but due to the presence of the carbon atoms in SiC, the density of states (D<sub>it</sub>) at the SiC/SiO<sub>2</sub> interface is higher [24]–[27]. According to the carbon cluster model [28], the SiC/SiO<sub>2</sub> interface is a defect rich region populated by  $\pi$ -bonds, sp<sup>2</sup>-bonded carbon clusters, Near Interface Traps (NITs) and fixed charges (Q<sub>f</sub>). Significantly, NITs are acceptor-like defects characterized by fast trapping abilities [29] obstructing the transport of electrons in the channel, eventually resulting in poor performance, whilst raising oxide reliability concerns [30]

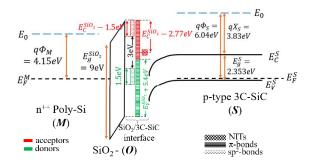

In 4H-SiC MOSFETs, NITs are located within the band gap close to  $E_C$  and largely affect the channel mobility [29], [31], [32]. Recent research suggests that more elaborate gate oxide fabrication processes (e.g. forming a SiO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> gate stack) are required to reduce the defects at the 4H-SiC/SiO<sub>2</sub> interface, the defects [33]. This is not needed for the 3C-SiC/SiO<sub>2</sub> interface. As shown in Fig. 1, for a 3C-SiC/SiO2 n-MOS structure the NITs and all the acceptor-like traps are above the conduction band ( $E_C$ ) of 3C-SiC [34]–[36]. Consequently, only Q<sub>f</sub> and donor-like traps ( $\pi$ -bonds and sp<sup>2</sup>

Fig. 1 Energy band diagram for n-type 3C-SiC MOS at  $V_G = 0V$  showing the  $D_{it}^{3C-SiC/SiO_2}$  according to the carbon cluster model [28] for 3C-SiC/SiO\_2. The figure does not illustrate the acting  $Q_f^{3C-SiC}$ .

-bonds) can affect the electrical properties [37], [38]. In addition to existing  $Q_f$ , ionized donor-like states are highly likely to be occupied by a hole and hence also act as fixed positive charges at the interface. Nonetheless, the position of the Fermi-level ( $E_F$ ) at the interface during thermal equilibrium defines only a limited part of donor-like  $D_{it}^{3C-SiC/SiO_2}$  to be energetically above it (i.e. they are ionized). In addition, with application of positive bias on the gate, the amount of ionized  $D_{it}^{3C-SiC/SiO_2}$  reduces because the bands at the interface bend further downwards. Therefore, the importance of  $D_{it}^{3C-SiC/SiO_2}$  on affecting the mobility of electrons in the channel of 3C-SiC n-MOS devices can be considered negligible compared to the effect from  $Q_f$  [29], [39], [40].

## III. 3C - SIC/SIO<sub>2</sub> Channel Mobility Model

The mobility of electrons in the channel can be modelled by deploying Matthiessen's rule as a weighted summation of different mobility components (1). These include the bulk mobility ( $\mu_{bulk}^{3C-SiC}$ ), acoustic phonon scattering ( $\mu_{ac}^{3C-SiC}$ ), surface roughness scattering ( $\mu_{SR}^{3C-SiC}$ ) and coulomb scattering on Q<sub>f</sub> and ionized traps at the interface ( $\mu_{cb}^{3C-SiC}$ ). In (1), D is a damping parameter defined as  $D = e^{-x/l_{crit}}$ , where x is the distance from the interface and  $l_{crit}$  is a fitting parameter. D ensures that the inversion layer terms on calculating the corresponding mobility degradation elements are switched off far from the channel region area.

$$\frac{1}{\mu_{ch}} = \frac{1}{\mu_{bulk}} + \frac{D}{\mu_{ac}} + \frac{D}{\mu_{SR}} + \frac{1}{\mu_{cb}}$$

(1)

The parameters and models used for  $\mu_{bulk}^{3C-SiC}$ , which comprises the mobility dependence on doping  $(\mu_{dop}^{3C-SiC})$  and electric field parallel to the current flow  $(\mu_{E//}^{3C-SiC})$ , are those in [12]. The focus of this work is on the remaining contributions in (1) which describe the mobility reduction at the semiconductor/oxide interface, where the transverse electric field  $(E_{\perp})$  is the driving force. The Lombardi equations (2), (3) and (4) [41] are utilized to model the  $\mu_{ac}^{3C-SiC}$ .

$$\mu_{ac} = \frac{B}{E_{\perp}} + \frac{CN_{A}^{\lambda}}{E_{\perp}^{1/3} \left(\frac{T}{300}\right)^{k_{1}}}$$

(2)

$$\mu_{SR} = \left(\frac{E_{\perp}^{A^*}}{\delta} + \frac{E_{\perp}^3}{\eta}\right)^{-1} \tag{3}$$

$$A^* = A_{init} + \frac{(\alpha_{\perp,n} n + \alpha_{\perp,p} p) N_{ref}^{\beta}}{N_A^{\beta}}$$

(4)

$$\mu_{cb} = \frac{\mu_1 \left(\frac{T}{300}\right)^{k_2} \left\{ 1 + \left[ n / \left( n_{trans} \left(\frac{Q_f}{N_0}\right)^{\eta_1} \right) \right]^p \right\}}{\left(\frac{Q_f}{N_0}\right)^{\eta_2} e^{-(d_{init}/l_{crit})} \left( 1 - e^{-\left(E_\perp/E_0\right)^{\gamma}} \right)}$$

(5)

## IV. MODEL PARAMETERS AT 300K

The parameters affecting the electrical performance of a MOS- structure include the p-body doping (N<sub>A</sub>), the oxide thickness (T<sub>ox</sub>), the gate metal workfunction ( $\Phi_M$ ) and the Q<sub>f</sub>. The analysis and incorporation of the carbon cluster model for the case of 3C-SiC/SiO<sub>2</sub>, conducted in Section II, suggest that the impact of D<sub>it</sub> is minor, and has thus been omitted. On calibrating the mobility model (1) for 3C-SiC n-MOS interfaces at 300K, two sets of measurements are employed from n-MOS devices having different designs.

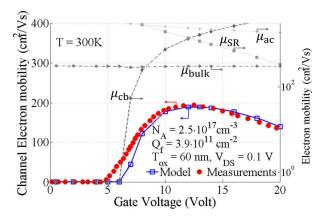

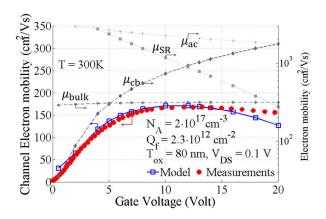

Device **n-MOS A** is a 3C-SiC n-MOS structure featuring poly-Si as gate metal,  $T_{ox}^A = 60nm \text{ SiO}_2$  gate oxide and  $Q_{f,A}^{3C-SiC} = 3.9 \times 10^{11} cm^{-2}$ , whilst  $N_A^A$  is not provided [19]. Device **n-MOS B** comprises a 3C-SiC grown on Si (3C-SiCon-Si) n-MOS with poly-Si as gate metal,  $N_A^B = 2 \times 10^{17} cm^{-3}$  and  $T_{ox}^B = 80nm$  SiO2 gate oxide, whilst the  $Q_{f,B}^{3C-SiC}$  is not provided [20]. The measured channel mobility ( $\mu_{ch}$ ) as a function of the applied gate voltage ( $V_G$ ) for the two MOS structures is given in Fig. 2 and Fig. 3. The gate threshold voltage ( $V_{th}$ ) for this work is determined to be the  $V_G$  at the onset of inversion, (i.e. where the mobility value becomes non-zero) in the  $\mu_{ch} - V_G$  plots. For n-MOS A  $V_{th}^A \approx 5V$  and for n-MOS B  $V_{th}^A \approx -0.5V$ . The  $N_A^A$  and  $Q_{f,B}$ values are then calculated, using (6)-(9) and the material parameter information of Table I to be  $N_A^A = 2.5 \times 10^{17} \text{ cm}^{-3}$  and  $Q_{f,B} = 2.3 \times 10^{12} \text{ cm}^{-2}$ .

$$V_{th} = V_{FB} + \frac{T_{0x}|Q_{inv}|}{\epsilon_{ox}} + \Phi_t$$

(6)

Fig. 2 Channel mobility as a function of gate voltage at 300K for n-MOS A. Simulations results of the channel mobility ( $\Box$ ) and the components of mobility (grey) using the derived model are compared to measurements (•) obtained from [19].

Fig. 3 Channel mobility as a function of gate voltage at 300K for n-MOS B. Simulations results of the channel mobility ( $\Box$ ) and the components of mobility (grey) using the derived model are compared to measurements (•) obtained from [20]

$$\Phi_t = 2\frac{kT}{q} \ln \frac{N_A}{n_i} \tag{7}$$

$$V_{FB} = \Phi_M - \left(\chi_S + \frac{E_g^S}{2} + \frac{\Phi_t}{2}\right) - \frac{T_{ox}qQ_f}{\epsilon_{ox}}$$

(8)

$$|Q_{inv}| = \sqrt{2q\epsilon_S N_A \Phi_t} \tag{9}$$

TABLE I.

PARAMETERS USED IN THE CALCULATION OF THRESHOLD VOLTAGE

| Parameter                  | Material         | Value                                                    |

|----------------------------|------------------|----------------------------------------------------------|

| $\Phi_M(eV)$               | N – Polysilicon  | 4.15 ª                                                   |

| $\chi_s(eV)$               | 3C-SiC           | 3.83 <sup>b</sup>                                        |

| $E_g^{S}(eV)$              | 3C-SiC           | 2.35 <sup>b</sup>                                        |

| $n_i (cm^{-3})$            | 3C-SiC           | 2.285×10 <sup>-1 b</sup>                                 |

| $\epsilon_{s} (Fcm^{-1})$  | 3C-SiC           | 0.8606×10 <sup>-12 b</sup>                               |

| $\epsilon_{ox} (Fcm^{-1})$ | SiO <sub>2</sub> | 0.3453×10 <sup>-12 c</sup>                               |

| L                          |                  | <sup>a.</sup> [42] <sup>b.</sup> [11] <sup>c.</sup> [43] |

To derive the parameter values presented in Table II for (2), (3), (4) and (5), precise geometric and electro-physical models of devices MOS A and B were developed using Synopsys TCAD. The properties of bulk 3C - SiC were modelled using the material physics equations and parameters discussed in [11]. The equations (2), (3), (4) and (5) were incorporated and the equivalent parameter values used for Silicon MOS devices were used as the initial model condition. Following, V<sub>G</sub> was ramped from 0 to 20V and concurrently, the mobility driving forces  $(E_{\perp}, E_{\parallel})$ , the density of free electrons (n) and the density of free holes (p) at the channel region were monitored and recorded.  $\mu_{ch}$  and the individual mobility components were then calculated as a function of V<sub>G</sub> and the simulation results were overlayed and compared with the equivalent measurements. The procedure was repeated with the parameters altered one by one to study how they influence  $\mu_{ch}(V_G)$  and the individual mobility components, which allowed for the informed adjustment of the parameter values during each subsequent iteration. After multiple iterations an acceptable fit between model predictions and

measurements was achieved for both devices (depicted in Fig. 2 and Fig. 3).

The simulations show that at low voltages the coulomb scattering mobility ( $\mu_{cb}$ ) component dominates, whereas at higher voltages the combined effect of surface scattering ( $\mu_{SR}$ ) and bulk mobility ( $\mu_{bulk}$ ) dominates. As the gate voltage increases further, surface scattering dominates. As depicted, the model slightly overestimates the  $\mu_{cb}$  component for the n-MOS A case whereas it slightly overestimates the  $\mu SR$  term for the case of n-MOS B. When considering the rather wide range of applied gate voltages examined and the large dissimilarity of the two structures used for the model parameters derivation, the overall model prediction can be considered sufficiently credible for general use with 3C-SiC n-MOS devices.

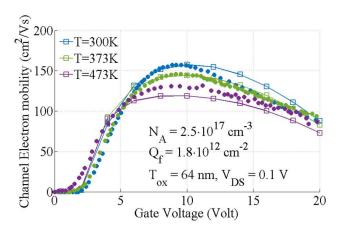

## V. TEMPERATURE DEPENDENCE

The temperature dependence of the proposed mobility model makes use of measurements from a third MOS structure, MOS C [21]. MOS C has identical epilayers with those of MOS A (i.e.  $N_A^C = N_A^A$ ). Its oxide thickness is  $T_{ox} = 64nm$  whereas from the measurements shown in Fig. 4 it can be estimated that  $V_{th}^C \approx 1.5V$ . From (6)-(9) the fixed charge at the interface is calculated  $Q_{f,C}^{3C-SiC} = 1.8 \times 10^{12} cm^{-2}$ . By following the same procedure described in Section IV, the model parameters  $k_1$ and  $k_2$  listed in Table II have been derived. As shown, in Fig. 4 the predictions are in sufficient agreement with the measurements for the temperature range 300K - 473K, with the model moderately overestimating the mobility at 300K and moderately underestimating it at 473K.

Fig. 4 Channel mobility as a function of gate voltage between 300K and 473K for n-MOS C. Simulations results using the derived model  $(\Box)$  are compared to measurements (•) obtained from [21]

TABLE II.

PARAMETER VALUES OF THE CHANNEL MOBILITY MODEL

| Parameter                                                                     | Eq. | Value              |

|-------------------------------------------------------------------------------|-----|--------------------|

| $B (cm  s^{-1})$                                                              | (2) | $5 \times 10^{8}$  |

| $\begin{array}{c} C\\ (cm^{\frac{5}{3}} V^{-\frac{2}{3}} s^{-1}) \end{array}$ | (2) | $5 \times 10^{2}$  |

| λ                                                                             | (2) | 0.1                |

| $\frac{\delta}{(cm^2V^{-1}s^{-1})}$                                           | (3) | $5 \times 10^{16}$ |

| $\eta$<br>(V <sup>2</sup> cm <sup>-1</sup> s <sup>-1</sup> )                  | (3) | $3 \times 10^{20}$ |

| A <sub>init</sub>                                  | (4) | 2.1                    |

|----------------------------------------------------|-----|------------------------|

| $lpha_{\perp,n}\ (cm^3)$                           | (4) | $6.85 \times 10^{-21}$ |

| $lpha_{\perp,p}\ (cm^3)$                           | (4) | $6.85 \times 10^{-21}$ |

| $N_{ref} (cm^{-3})$                                | (4) | 1                      |

| β                                                  | (4) | 0.092                  |

| <i>k</i> <sub>1</sub>                              | (2) | 5                      |

| $ \begin{array}{c} E_0 \\ (Vcm^{-1}) \end{array} $ | (5) | $1 \times 10^{-6}$     |

| $N_0 (cm^{-2})$                                    | (5) | $1 \times 10^{11}$     |

| γ                                                  | (5) | 1                      |

| $(cm^2V^{-1}s^{-1})$                               | (5) | 1                      |

| $n_{trans}$<br>( $cm^{-3}$ )                       | (5) | $2 \times 10^{16}$     |

| $\eta_1$                                           | (5) | 0.1                    |

| $\eta_2$                                           | (5) | 0.4                    |

| υ                                                  | (5) | 1.2                    |

| d <sub>init</sub> (cm)                             | (5) | $5 \times 10^{-8}$     |

| l <sub>crit</sub> (cm)                             | (5) | $7 \times 10^{-7}$     |

| k2                                                 | (5) | 1.5                    |

## VI. CONCLUSIONS

In this work, a comprehensive model of the mobility of electrons at the 3C-SiC/SiO<sub>2</sub> inversion layer was developed and validated with measurements obtained from three MOS structures with dissimilar characteristics. The derived channel mobility model employs Matthiessen's rule to incorporate the influence of acoustic phonon scattering, surface roughness scattering and coulomb scattering due to fixed charges and ionized traps at the interface. The models of 3C-SiC bulk mobility (doping and field dependence) which were the subject of a previous study are also incorporated. It has been shown to predict the channel mobility for gate voltages ranging 0 - 20 V and temperatures ranging 300 – 473 K with reasonable accuracy. Since the channel region is considered an important contributor in the total resistance (R<sub>DS(on</sub>) of MOS-based devices, and considering the previous unavailability of appropriate 3C-SiC/SiO<sub>2</sub> models for TCAD simulations, this work enables more accurate and informative modelling and optimization of 3C-SiC MOS devices.

#### REFERENCES

- A. A. Lebedev, S. P. Lebedev, V. Y. Davydov, S. N. Novikov, and Y. N. Makarov, "Growth and investigation SiC based heterostructures," in 2016 15th Biennial Baltic Electronics Conference (BEC), Oct. 2016, pp. 4–5. doi: 10.1109/BEC.2016.7743717.

- [2] M. Krieger, G. Pensl, M. Bakowski, A. Schöner, H. Nagasawa, and M. Abe, "Hall Effect in the Channel of 3C-SiC MOSFETs," *Mater. Sci. Forum*, pp. 441–444, May 2005, doi: 10.4028/www.scientific.net/MSF.483-485.441.

- [3] Jianwei Wan, M. A. Capano, M. R. Melloch, and J. A. Cooper, "Nchannel 3C-SiC MOSFETs on silicon substrate," *IEEE Electron Device Lett.*, vol. 23, no. 8, pp. 482–484, Aug. 2002, doi: 10.1109/LED.2002.801259.

- [4] T. Ohshima et al., "The Electrical Characteristics of Metal-Oxide-Semiconductor Field Effect Transistors Fabricated on Cubic Silicon Carbide," Jpn. J. Appl. Phys., vol. 42, no. Part 2, No. 6B,

pp. L625-L627, Jun. 2003, doi: 10.1143/JJAP.42.L625.

- [5] Kin Kiong Lee, Y. Ishida, T. Ohshima, K. Kojima, Y. Tanaka, T. Takahashi, H. Okumura, K. Arai, and T. Kamiya, "N-channel MOSFETs fabricated on homoepitaxy-grown 3C-SiC films," *IEEE Electron Device Lett.*, vol. 24, no. 7, pp. 466–468, Jul. 2003, doi: 10.1109/LED.2003.815006.

- [6] F. Li, F. Roccaforte, G. Greco, P. Fiorenza, F. La Via, A. Pérez-Tomas, J. E. Evans, C. A. Fisher, F. A. Monaghan, P. A. Mawby, and M. Jennings, "Status and prospects of cubic silicon carbide power electronics device technology," *Materials (Basel).*, vol. 14, no. 19, Oct. 2021, doi: 10.3390/MA14195831.

- H. Nagasawa and K. Yagi, "3C-SiC Single-Crystal Films Grown on 6-Inch Si Substrates," *Phys. status solidi*, vol. 202, no. 1, pp. 335–358, Jul. 1997, doi: 10.1002/1521-3951(199707)202:1<335::AID-PSSB335>3.0.CO;2-Y.

- [8] H. Nagasawa, M. Abe, K. Yagi, T. Kawahara, and N. Hatta, "Fabrication of high performance 3C-SiC vertical MOSFETs by reducing planar defects," *Phys. status solidi*, no. 7, pp. 1272–1280, Jul. 2008, doi: 10.1002/pssb.200844053.

- [9] A. Arvanitopoulos, S. Perkins, K. N. Gyftakis, M. Antoniou, and N. Lophitis, "3C-SiC material parameters for accurate TCAD modeling and simulation," in *The 10th International Conference* on Silicon Epitaxy and heterostructures – ICSI10, 2017, pp. 115– 116.

- [10] A. Arvanitopoulos, N. Lophitis, S. Perkins, K. N. Gyftakis, M. Belanche Guadas, and M. Antoniou, "Physical parameterisation of 3C-Silicon Carbide (SiC) with scope to evaluate the suitability of the material for power diodes as an alternative to 4H-SiC," in 2017 IEEE 11th International Symposium on Diagnostics for Electrical Machines, Power Electronics and Drives (SDEMPED), Aug. 2017, vol. 2017-Janua, no. 3, pp. 565–571. doi: 10.1109/DEMPED.2017.8062411.

- [11] A. Arvanitopoulos, N. Lophitis, K. N. Gyftakis, S. Perkins, and M. Antoniou, "Validated physical models and parameters of bulk 3C-SiC aiming for credible Technology Computer Aided Design (TCAD) simulation," *IOP Semicond. Sci. Technol.*, vol. 32, no. 10, p. 104009, Oct. 2017, doi: 10.1088/1361-6641/aa856b.

- N. Lophitis, A. Arvanitopoulos, S. Perkins, and M. Antoniou, "TCAD Device Modelling and Simulation of Wide Bandgap Power Semiconductors," in *Disruptive Wide Bandgap Semiconductors, Related Technologies, and Their Applications*, Y. K. Sharma, Ed. Rijeka: InTech, 2018. doi: 10.5772/intechopen.76062.

- [13] A. E. Arvanitopoulos, M. Antoniou, S. Perkins, M. Jennings, M. B. Guadas, K. N. Gyftakis, and N. Lophitis, "On the Suitability of 3C-Silicon Carbide as an Alternative to 4H-Silicon Carbide for Power Diodes," *IEEE Trans. Ind. Appl.*, vol. 55, no. 4, pp. 4080–4090, Jul. 2019, doi: 10.1109/TIA.2019.2911872.

- [14] A. Arvanitopoulos, S. Perkins, K. N. Gyftakis, N. Lophitis, M. R. Jennings, and M. Antoniou, "Carrier Transport mechanisms contributing to the sub-threshold current in 3C-SiC-on-Si Schottky Barrier Diodes," in 2018 1st Workshop on Wide Bandgap Power Devices and Applications in Asia (WiPDA Asia), May 2018, pp. 169–173. doi: 10.1109/WiPDAAsia.2018.8734538.

- [15] A. Arvanitopoulos, M. Antoniou, F. Li, M. R. R. Jennings, S. Perkins, K. N. N. Gyftakis, and N. Lophitis, "Viable 3C-SiC-on-Si MOSFET design disrupting current Material Technology Limitations," in 2019 IEEE 12th International Symposium on Diagnostics for Electrical Machines, Power Electronics and Drives (SDEMPED), Aug. 2019, pp. 364–370. doi: 10.1109/DEMPED.2019.8864910.

- [16] A. E. Arvanitopoulos, M. Antoniou, M. R. Jennings, S. Perkins, K. N. Gyftakis, P. Mawby, and N. Lophitis, "A Defects-Based Model on the Barrier Height Behavior in 3C-SiC-on-Si Schottky Barrier Diodes," *IEEE J. Emerg. Sel. Top. Power Electron.*, vol. 8, no. 1, pp. 54–65, Mar. 2020, doi: 10.1109/JESTPE.2019.2942714.

- [17] A. Arvanitopoulos, M. Antoniou, F. Li, M. R. Jennings, S. Perkins, K. N. Gyftakis, and N. Lophitis, "3C-SiC-on-Si MOSFETs: Overcoming Material Technology Limitations," *IEEE Trans. Ind. Appl.*, vol. 58, no. 1, pp. 565–575, Jan., doi: 10.1109/TIA.2021.3119269.

- [18] A. Arvanitopoulos, F. Li, M. R. Jennings, S. Perkins, K. Gyftakis, P. Mawby, M. Antoniou, and N. Lophitis, "Experimental and

Physics-Based Study of the Schottky Barrier Height Inhomogeneity and Associated Traps Affecting 3C-SiC-on-Si Schottky Barrier Diodes," *IEEE Trans. Ind. Appl.*, vol. 57, no. 5, pp. 5252–5263, Sep. 2021, doi: 10.1109/TIA.2021.3087667.

- [19] M. Kobayashi, H. Uchida, A. Minami, T. Sakata, R. Esteve, and A. Schöner, "3C-SiC MOSFET with High Channel Mobility and CVD Gate Oxide," *Mater. Sci. Forum*, vol. 679–680, pp. 645–648, Mar. 2011, doi: 10.4028/www.scientific.net/MSF.679-680.645.

- [20] Jianwei Wan, M. A. Capano, M. R. Melloch, and J. A. J. Cooper, "Inversion channel MOSFETs in 3C-SiC on silicon," in Proceedings. IEEE Lester Eastman Conference on High Performance Devices, 2002, pp. 83–89. doi: 10.1109/LECHPD.2002.1146735.

- [21] H. Uchida, A. Minami, T. Sakata, H. Nagasawa, and M. Kobayashi, "High Temperature Performance of 3C-SiC MOSFETs with High Channel Mobility," *Mater. Sci. Forum*, vol. 717–720, pp. 1109–1112, May 2012, doi: 10.4028/www.scientific.net/MSF.717-720.1109.

- [22] R. P. Ramamurthy, D. T. Morisette, V. Amarasinghe, and L. C. Feldman, "Thermal-oxidation-free dielectrics for SiC power devices," in 2017 IEEE 5th Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Oct. 2017, pp. 242–245. doi: 10.1109/WiPDA.2017.8170554.

- [23] P. Friedrichs, E. P. Burte, and R. Schörner, "Dielectric strength of thermal oxides on 6H-SiC and 4H-SiC," *Appl. Phys. Lett.*, vol. 65, no. 13, pp. 1665–1667, Sep. 1994, doi: 10.1063/1.112904.

- [24] T. Billon, E. Bano, L. Di Cioccio, T. Ouisse, P. Lassagne, and C. Jaussaud, "Electrical and physico-chemical characterizations of the interface," *Microelectron. Eng.*, vol. 28, no. 1–4, pp. 193–196, Jun. 1995, doi: 10.1016/0167-9317(95)00041-6.

- P. Friedrichs, E. P. Burte, and R. Schörner, "Interface properties of metal-oxide-semiconductor structures on n -type 6H and 4H-SiC," *J. Appl. Phys.*, vol. 79, no. 10, pp. 7814–7819, May 1996, doi: 10.1063/1.362389.

- [26] L. A. Lipkin and J. W. Palmour, "Improved oxidation procedures for reduced SiO2/SiC defects," *J. Electron. Mater.*, vol. 25, no. 5, pp. 909–915, May 1996, doi: 10.1007/BF02666657.

- [27] J. N. Shenoy, J. A. Cooper, and M. R. Melloch, "Comparison of thermally oxidized metal–oxide–semiconductor interfaces on 4H and 6H polytypes of silicon carbide," *Appl. Phys. Lett.*, vol. 68, no. 6, pp. 803–805, Feb. 1996, doi: 10.1063/1.116538.

- [28] M. Bassler, G. Pensl, and V. Afanas'ev, "'Carbon cluster model' for electronic states at interfaces," *Diam. Relat. Mater.*, vol. 6, no. 10, pp. 1472–1475, Aug. 1997, doi: 10.1016/S0925-9635(97)00074-5.

- [29] V. V. Afanas'ev, F. Ciobanu, S. Dimitrijev, G. Pensl, and A. Stesmans, "SiC/SiO2 Interface States: Properties and Models," *Mater. Sci. Forum*, vol. 483–485, pp. 563–568, May 2005, doi: 10.4028/www.scientific.net/MSF.483-485.563.

- [30] H. A. Moghadam, S. Dimitrijev, J. S. Han, A. Aminbeidokhti, and D. Haasmann, "Quantified Density of Active near Interface Oxide Traps in 4H-SiC MOS Capacitors," *Mater. Sci. Forum*, vol. 858, pp. 603–606, May 2016, doi: 10.4028/www.scientific.net/MSF.858.603.

- [31] S. Nakazawa, T. Okuda, J. Suda, T. Nakamura, and T. Kimoto, "Interface Properties of 4H-SiC (112<sup>-0</sup>) and (11<sup>-00</sup>) MOS Structures Annealed in NO," *IEEE Trans. Electron Devices*, vol. 62, no. 2, pp. 309–315, Feb. 2015, doi: 10.1109/TED.2014.2352117.

- [32] D. Okamoto, H. Yano, T. Hatayama, and T. Fuyuki, "Development of 4H-SiC MOSFETs with Phosphorus-Doped Gate Oxide," *Mater. Sci. Forum*, vol. 717–720, pp. 733–738, May 2012, doi: 10.4028/www.scientific.net/MSF.717-720.733.

- [33] F. Arith, J. Urrcsti, K. Vasilevskiy, S. Oisenl, N. Wright, and A. O'Neill, "High Mobility 4H-SiC MOSFET Using a Thin SiO2/Al2O3 Gate Stack," in 2018 48th European Solid-State Device Research Conference (ESSDERC), Sep. 2018, pp. 30–33. doi: 10.1109/ESSDERC.2018.8486896.

- [34] A. Schöner, M. Krieger, G. Pensl, M. Abe, H. Nagasawa, B. A. Schöner, M. Krieger, G. Pensl, M. Abe, H. Nagasawa, A. Schöner, M. Krieger, G. Pensl, M. Abe, and H. Nagasawa, "Fabrication and Characterization of 3C-SiC-Based MOSFETs," *Chem. Vap.*

*Depos.*, vol. 12, no. 8–9, pp. 523–530, Sep. 2006, doi: 10.1002/cvde.200606467.

- [35] G. Pensl, M. Bassler, F. Ciobanu, V. Afanas'ev, H. Yano, T. Kimoto, and H. Matsunami, "Traps at the SiC/SiO 2 -Interface," *MRS Proc.*, vol. 640, p. H3.2, Mar. 2000, doi: 10.1557/PROC-640-H3.2.

- [36] F. Ciobanu, G. Pensl, H. Nagasawa, A. Schöner, S. Dimitrijev, K. Y. Cheong, V. V. Afanas'ev, and G. Wagner, "Traps at the Interface of 3C-SiC/SiO2-MOS-Structures," *Mater. Sci. Forum*, vol. 433–436, pp. 551–554, Sep. 2003, doi: 10.4028/www.scientific.net/MSF.433-436.551.

- [37] R. Esteve, "Fabrication and Characterization of 3C- and4H-SiC MOSFETs," KTH Royal Institute of Technology, 2011.

- [38] V. V. Afanasev, M. Bassler, G. Pensl, and M. Schulz, "Intrinsic SiC/SiO2 Interface States," *Phys. status solidi*, vol. 162, no. 1, pp. 321–337, Jul. 1997, doi: 10.1002/1521-396X(199707)162:1<321::AID-PSSA321>3.0.CO;2-F.

- [39] K. Cherkaoui, A. Blake, Y. Y. Gomeniuk, J. Lin, B. Sheehan, M. White, P. K. Hurley, and P. J. Ward, "Investigating positive oxide charge in the SiO 2 /3C-SiC MOS system," *AIP Adv.*, vol. 8, no. 8, p. 085323, Aug. 2018, doi: 10.1063/1.5030636.

- [40] F. Li, S. Qiu, M. R. Jennings, and P. A. Mawby, "Fabrication and Dielectric Breakdown of 3C-SiC/SiO 2 MOS Capacitors," in 2019 IEEE 12th International Symposium on Diagnostics for Electrical Machines, Power Electronics and Drives (SDEMPED), Aug. 2019, pp. 344–350. doi: 10.1109/DEMPED.2019.8864836.

- [41] C. Lombardi, S. Manzini, A. Saporito, and M. Vanzi, "A physically based mobility model for numerical simulation of nonplanar devices," *IEEE Trans. Comput. Des. Integr. Circuits Syst.*, vol. 7, no. 11, pp. 1164–1171, 1988, doi: 10.1109/43.9186.

- [42] J. Choi, J.-S. Yoon, and C.-K. Baek, "Investigation of DC Characteristics in Polysilicon Nanowire Tunneling Field-Effect Transistors," *J. Nanosci. Nanotechnol.*, vol. 17, no. 5, pp. 3071– 3076, May 2017, doi: 10.1166/jnn.2017.14047.

- [43] C. Wyon, "Future technology for advanced MOS devices," Nucl. Instruments Methods Phys. Res. Sect. B Beam Interact. with Mater. Atoms, vol. 186, no. 1–4, pp. 380–391, Jan. 2002, doi: 10.1016/S0168-583X(01)00908-9.