# Power Density Optimization of a DC/DC Converter for an Aircraft Supercapacitors Energy Storage

Niklas Fritz, Mohamed Rashed and Christian Klumpner

The Department of Electrical and Electronic Engineering

The University of Nottingham, United Kingdom

niklas.fritz@rwth-aachen.de, mohamed.rashed@nottingham.ac.uk, christian.klumpner@nottingham.ac.uk

Abstract—This paper presents a computationally efficient design algorithm for a DC/DC converter, optimized for power density. Interleaving and series-connecting of several converter cells is included in the analysis. The choice of the converter design parameters, such as the semiconductor devices or the number of interleaved converter cells may have unpredictable impacts on the resulting power density. Therefore, fully analytical models of the operating waveforms, the converter losses and also the converter weight are introduced. Using those models, an algorithm is developed to optimize a 2 kW DC/DC converter for an aircraft supercapacitors energy storage system.

Index Terms—Synchronous Buck Converter, Modelling, Optimization, Power density, Supercapacitor, More Electric Aircraft

#### I. INTRODUCTION

The More Electric Aircraft (MEA) is a new concept in the development of next-generation aircrafts [1, 2]. Traditional hydraulic and pneumatic actuators used to drive critical flying surfaces are increasingly replaced by electrical systems, which have the potential to be significantly more efficient and light-weight, which would reflect in lower fuel consumption. However, adopting the MEA concept imposes challenges to the design of the electrical power system as its power rating significantly increases. Therefore, it is crucial that the electrical components are optimized for power density.

This work is related to the design of a supercapacitor energy storage system which is needed to smoothen the ripple of the power system, deal with regeneration and enhance the power surge capability. The system will consist of a supercapacitor stack, interfaced with the aircraft's 270 V DC bus via a bidirectional non-isolated DC/DC converter and the synchronous buck converter has been chosen as the preferred topology for this study. In addition to the generic topology, more complex variants such as interleaved (parallel channels) and cascaded (series connection of cells) converters are considered.

Deciding on design parameters of the converter is a complex task. The choice of semiconductor devices, the number of interleaved half bridges, the amount of inductance, the switching frequency, all those parameters have great influence on power density which are hard to predict. The approach in this paper helps to establish a link of analytical equations between the design variables and the power density.

The synchronous buck converter, although being a hardswitched topology, has been shown to achieve attractive power densities [3, 4] when using wide-bandgap (WBG) power semiconductors operating at hundreds of kHz which enables minimization of magnetics whilst the cooling requirements remain reasonable due to the lower switching losses.

Analytical models providing an evaluation of current and voltage waveforms in this topology and the evaluation of the losses have been investigated in [5-7], also weight minimizations have been proposed in [7, 8]. The benefits of interleaving have been analyzed in [6, 9-11]. This paper adds the analysis of cascaded converters and further modelling of the converter weight. Moreover, the ripple charge of the input capacitor is analyzed for interleaved converters.

The optimization procedure in this work is based on fully analytical modelling and consists of three layers, as proposed in [12]: First, the converter current waveforms are analyzed and key variables, such as for example RMS or ripple currents, are derived. Based on these, an analytical loss model of both active and passive components is developed. A model to estimate the weight of the main components is added, which, for example, links the converter losses to the weight of the required cooling system.

As the adopted models are fully analytical, there is no need to run time-consuming simulations in time domain. Hence, the major advantage of this technique is its speed in calculation whilst being able to assess a wide range of design configurations. This approach has some limitations, for example the high-frequency losses in the magnetics, which are difficult to assess analytically.

The paper is structured as follows: In section II, the synchronous buck converter topology and its variations are introduced. Sections III, IV and V demonstrate the modelling of the operating waveforms, the losses and the weight, respectively. Section VI presents the optimization procedure. In section VII, the results are summarized and the conclusions are presented in section VIII.

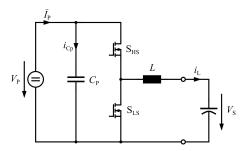

Figure 1: The generic synchronous buck converter topology

#### **II. THE SYNCHRONOUS BUCK CONVERTER**

In Fig. 1, the generic synchronous buck converter is shown. In the following, all current and voltage equations will be related to the directions introduced in Fig. 1. The supercapacitor system is modeled as an ideal voltage source  $V_{\rm S}$ . A positive power transfer means charging the supercapacitor from the DC bus  $V_{\rm P}$  and a negative power transfer means discharging the supercapacitor into the DC bus. The basic requirements and assumptions about this application are summarized as follows:

- The rated power of the converter is  $P = 2 \,\mathrm{kW}$

- The DC bus is the 270 V DC bus in aircraft, fulfilling the requirements of Mil-Std-704F [13]

- The supercapacitor stack consists of k cells connected in series. Each cell is assumed to be fully charged at  $V_{cell} = 2.50 \text{ V}$ . Additionally, the supercapacitor shall discharge to 50% of the maximum voltage, which corresponds to a minimum cell voltage of 1.25 V, to avoid increasing the output current and hence, losses. This will guarantee an energy extraction of 75% of nominal energy stored.

- Three supercapacitor stack configurations are analyzed, having a different number k of series-connected cells and thus, different rated voltage ranges V<sub>S</sub>:

- 1)  $k = 24 \Longrightarrow V_{\rm S} = 30 \dots 60 \, {\rm V}$

- 2)  $k = 48 \Longrightarrow V_{\rm S} = 60 \dots 120 \,\mathrm{V}$

- 3)  $k = 96 \Longrightarrow V_{\rm S} = 120 \dots 240 \,\mathrm{V}$

- Interleaving of parallel converters is considered for  $N = 1 \dots 3$  half bridges

- Cascading series-connected converters is considered for M = 1, 2, 4 half bridges

## A. Interleaving

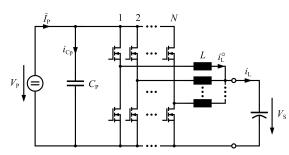

Interleaving is a concept used in power electronic converters [9, 10]. The interleaved variant of the synchronous buck converter is shown in Fig. 2.

Figure 2: The interleaved synchronous buck converter topology

Instead of processing all of the supercapacitor current with only one converter, it is shared between N paralleled phases, which individually operate more efficiently. Additionally, the PWM patterns are phase-shifted in time. This way, the ripple currents of each interleaved phase, as seen from both the supercapacitor stack and the 270 V DC bus, partly cancel out. For the *j*'th phase, the time delay  $t_{d,j}$  is given as follows:

$$t_{\rm d,j} = \frac{j-1}{N} \cdot T_{\rm sw} \tag{1}$$

$T_{\rm sw}$  denotes the switching time period. The phase-shift also implies that the frequency  $f_{\rm sw,eff}$  of the supercapacitor and the input capacitor ripple currents is increased by a multiple Ncompared to the switching frequency  $f_{\rm sw}$  of the single phase:

$$f_{\rm sw,eff} = N \cdot f_{\rm sw} \tag{2}$$

At light load where usually efficiency drops, disabling some phases may facilitate an increase in efficiency as the remaining phases will operate at higher loading. This technique is called phase-shedding [5, 14].

## B. Cascading

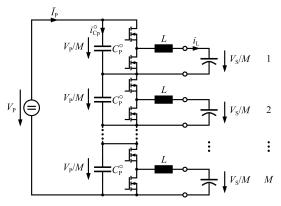

In addition to interleaving, also the series connection will be analyzed in this work. Fig. 3 shows the concept of cascading: The supercapacitor is split into M banks, which consist of

Figure 3: The cascaded synchronous buck converter topology

$^{1}/M$  the cells of the single module version. Even though the current rating is the same, the voltage stress on each half bridge and each inductor is reduced. This way, the inductance can be reduced to  $^{1}/M$ . By phase shifting the PWM patterns, the ripple voltages of each series input capacitor  $C_{\rm P}^{\circ}$  partly cancel out. Cascading is also useful in terms of redundancy as if one supercapacitor bank or converter cell fails, it could be bypassed externally. Also, independent control of power from each of the M stacks is possible which would lead to an enhanced management of voltage sharing in case a stack contains aged supercapacitor cells with imbalanced resistance or capacitance.

#### III. MODEL OF THE OPERATING WAVEFORMS

This section analyzes the current and voltage waveforms in the synchronous buck converter. The converter is idealized, i.e. ohmic resistances and voltage drops across diodes or switches are neglected. This significantly simplifies the equations. After that, the losses are calculated separately. The philosophy of this approach also reflects in simulation software [15].

## A. Interleaved Converter

First, the interleaved variant of the converter is analyzed. Each phase is operated with a PWM pattern, where d denotes the duty cycle. Quantities that relate to the individual phases are marked with a superscript circle, whereas quantities that relate to the common output which is connected to the

supercapacitor stack are unmarked. The current waveform in the inductor of each phase,  $i_{\rm L}^{\circ}(t)$ , is given in (3).

$$i_{\rm L}^{\circ}(t) = \begin{cases} \overline{I}_{\rm L}^{\circ} - \frac{1}{2}\Delta I_{\rm pp}^{\circ} + \frac{V_{\rm P} - V_{\rm S}}{L} \cdot t & \text{for } 0 \le t < dT_{\rm sw} \\ \overline{I}_{\rm L}^{\circ} + \frac{1}{2}\Delta I_{\rm pp}^{\circ} - \frac{V_{\rm S}}{L} \cdot (t - dT_{\rm sw}) \text{ for } dT_{\rm sw} \le t < T_{\rm sw} \end{cases}$$

$$(3)$$

The DC component of the inductor current,  $\overline{I}_{L}^{\circ}$ , may be freely adjusted and does not depend on the duty cycle *d*. The peak-to-peak ripple component of the inductor current,  $\Delta I_{pp}^{\circ}$ , is given as follows:

$$\Delta I_{\rm pp}^{\circ} = \frac{V_{\rm P} - V_{\rm S}}{f_{\rm sw}L} d = \frac{V_{\rm S}}{f_{\rm sw}L} (1 - d) = \frac{V_{\rm P}}{f_{\rm sw}L} d (1 - d) \quad (4)$$

The following assumptions are made: Steady-state operation is assumed and all N interleaved phases are assumed to share the total output current. For the duty cycle, this implies:

$$d = \frac{V_{\rm S}}{V_{\rm P}} = \frac{\overline{I}_{\rm P}}{\overline{I}_{\rm L}} = \frac{\overline{I}_{\rm P}}{N \cdot \overline{I}_{\rm L}^{\circ}}$$

(5)

The inductor current at the switching instants t = 0 and  $t = dT_{sw}$  is useful for calculating the switching losses. It is denoted  $I_{sw}^{\circ}$  and given as follows:

$$I_{\rm sw}^{\circ} = \overline{I}_{\rm L}^{\circ} \pm \frac{1}{2} \Delta I_{\rm pp}^{\circ} \tag{6}$$

By squaring (3) and integrating, the RMS current in the inductor,  $I_{\rm L}^{\circ}$  and the RMS currents in the high-side and low-side switch,  $I_{\rm HS}^{\circ}$  and  $I_{\rm LS}^{\circ}$ , are derived, which are required for the calculation of conduction losses:

$$I_{\rm L}^{\circ} = \sqrt{\left(\overline{I}_{\rm L}^{\circ}\right)^2 + \frac{1}{12} \left(\Delta I_{\rm pp}^{\circ}\right)^2} \tag{7}$$

$$I_{\rm LS}^{\circ} = \sqrt{d} \cdot I_{\rm L}^{\circ}, \quad I_{\rm HS}^{\circ} = \sqrt{1 - d} \cdot I_{\rm L}^{\circ} \tag{8}$$

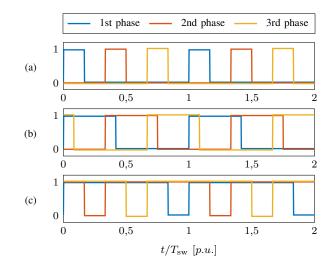

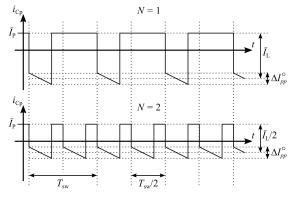

In the following, the ripple cancellation effect of interleaving is analyzed. The phase-shift of the PWM patterns results in a lower ripple current of the common output,  $\Delta I_{\rm pp}$ , compared to the ripple current in the inductors,  $\Delta I_{\rm pp}^{\circ}$ . A sample PWM pattern of N = 3 interleaved phases at different duty cycles is given in Fig. 4.

The following rules, inspired from [6, 10, 11], are derived:

- The waveforms are periodic with the time period  $\frac{T_{sw}}{N}$

- For a duration of  $\frac{T_{sw}}{N}(Nd \lfloor Nd \rfloor)$ , the output of a number of  $(\lfloor Nd \rfloor + 1)$  phases will be  $V_{\rm P}$ , while the remaining phases will be zero;

- For the remaining duration  $\frac{T_{sw}}{N}(1 Nd + \lfloor Nd \rfloor)$ , the output of a number of  $\lfloor Nd \rfloor$  phases will be  $V_{\rm P}$ , while the remaining phases will be zero.

These rules are used for calculating  $\Delta I_{\rm pp}$  as also presented in [10, 11]:

$$\Delta I_{\rm PP} = \int_0^{\frac{T_{\rm sw}}{N} (Nd - \lfloor Nd \rfloor)} \left( \sum_{j=1}^N \frac{\mathrm{d}i_{\mathrm{L},j}^\circ(t)}{\mathrm{d}t} \right) \cdot \mathrm{d}t$$

$$= \int_0^{\frac{T_{\rm sw}}{N} (Nd - \lfloor Nd \rfloor)} \frac{(\lfloor Nd \rfloor + 1) V_{\rm P} - NV_{\rm S}}{L} \cdot \mathrm{d}t$$

$$= \frac{V_{\rm P}}{N f_{\rm sw} L} \left( Nd - \lfloor Nd \rfloor \right) \left( 1 + \lfloor Nd \rfloor - Nd \right) \tag{9}$$

Figure 4: Sample PWM patterns for N = 3 interleaved phases. (a)  $d = \frac{1}{6}$ , (b)  $d = \frac{5}{12}$ , (c)  $d = \frac{5}{6}$ .

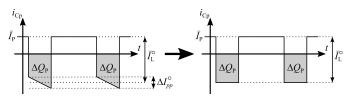

Similarly, this paper presents the calculation of the ripple of the primary DC bus capacitor charge  $\Delta Q_{\rm P}$  which is relevant for calculating the resulting DC bus voltage ripple. The current in this capacitor,  $i_{\rm CP}(t)$ , is shown in Fig. 5 for  $N = 1 \dots 2$ .

Figure 5: The DC bus capacitor current for different levels of interleaving

The trapezoidal shape of this waveform may be simplified to a square wave with an average current amplitude without any errors in the calculation of the ripple charge  $\Delta Q_{\rm P}$ . This situation is visualized in Fig. 6.

Figure 6: Simplification of the ripple charge calculation

Using the rules for interleaved phases, the capacitor current  $i_{C_P}(t)$  is expressed as given in (10).

$$i_{C_{P}}(t) = \begin{cases} \overline{I}_{P} - \overline{I}_{L}^{\circ} \cdot (\lfloor Nd \rfloor + 1) \\ \text{for } 0 \le t < \frac{T_{\text{sw}}}{N} \left( Nd - \lfloor Nd \rfloor \right) \\ \overline{I}_{P} - \overline{I}_{L}^{\circ} \cdot \lfloor Nd \rfloor \\ \text{for } \frac{T_{\text{sw}}}{N} \left( Nd - \lfloor Nd \rfloor \right) \le t < \frac{T_{\text{sw}}}{N} \end{cases}$$

(10)

By integration, the ripple charge  $\Delta Q_{\rm P}$  is calculated:

$$\Delta Q_{\rm P} = \int_{0}^{\frac{I_{\rm SW}}{N} (Nd - \lfloor Nd \rfloor)} -i_{\rm C_{\rm P}}(t) \cdot dt$$

$$= \frac{\overline{I}_{\rm P}}{f_{\rm sw}N} \left(1 - \frac{\lfloor Nd \rfloor}{Nd}\right) (1 + \lfloor Nd \rfloor - Nd) \qquad (11)$$

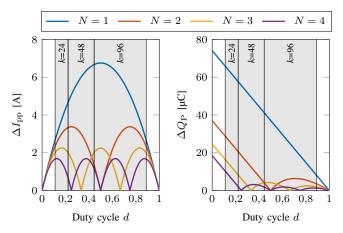

Fig. 7 shows a plot of the cumulated ripple quantities  $\Delta I_{\rm PP}$  and  $\Delta Q_{\rm P}$  for constant input voltage  $V_{\rm P}$  and current  $\overline{I}_{\rm P}$ . The supercapacitor system has a variable secondary voltage  $V_{\rm S}$ , depending on the number k of series connected cells. Therefore, a range of duty cycles has to be considered as represented by the shaded areas in Fig. 7. The largest ripples in that range of duty cycles need to be identified. Those worst case quantities will determine the required inductance L and capacitance  $C_{\rm P}$ .

Figure 7: Output ripple current and capacitor ripple charge for  $N = 1 \dots 4$ ,  $V_{\rm P} = 270 \text{ V}, \bar{I}_{\rm P} = 7.41 \text{ A}, L = 100 \,\mu\text{H}, f_{\rm sw} = 100 \,\mu\text{Hz}$ . Shaded: Range of duty cycles for the three investigated supercapacitor stack configurations.

From the input capacitor ripple charge  $\Delta Q_{\rm P}$ , it is possible to calculate the required capacitance for not exceeding a certain voltage deviation  $\Delta V_{\rm P}$  from the nominal DC voltage  $V_{\rm P}$ :

$$C_{\rm P} = \frac{\Delta Q_{\rm P,max}}{\Delta V_{\rm P}} \tag{12}$$

For the 270 V DC bus in aircraft, it is the Military Standard 704F that limits the ripple amplitude to  $\Delta V_{\rm P} \leq 6$  V [13]. Additionally, the peak energy  $E_{\rm C_P}$  that the primary capacitor has to carry can be easily calculated:

$$E_{\rm C_P} = \frac{1}{2}C_{\rm P} \left(V_{\rm P} + \Delta V_{\rm P}\right)^2 \tag{13}$$

#### B. Cascaded Converter

In addition to interleaving, cascading of M converter stages has similar benefits and in order to be able to compare these solutions, its analytical model will also be derived in this paper. The primary voltage is divided across M capacitors. If the capacitance of each individual capacitor is denoted  $C_{\rm P}^{\rm o}$ , the total equivalent primary capacitance  $C_{\rm P}$  is:

$$C_{\rm P} = \frac{C_{\rm P}^{\circ}}{M} \tag{14}$$

Cascading does not influence the output current ripple. On the DC bus side however, each half bridge creates a voltage ripple  $\Delta V_{\rm pp}^{\circ}$  in each primary capacitor  $C_{\rm P}^{\circ}$ . By phase-shifting the PWM pulse patterns of the cascaded half bridges, the overall primary ripple voltage  $\Delta V_{\rm pp}$  can be reduced. To compare this situation with interleaved operation, an equivalent primary ripple charge  $\Delta Q_{\rm P}$  is derived which charges and discharges the equivalent primary capacitance  $C_{\rm P}$  as given in (14):

$$\Delta V_{\rm PP} = \frac{\Delta Q_{\rm P}}{C_{\rm P}} = \int_0^{\frac{T_{\rm sw}}{M} (Md - \lfloor Md \rfloor)} \left( \sum_{j=1}^M \frac{-i_{\rm C_{\rm P}}^\circ(t)}{C_{\rm P}^\circ} \right) \cdot \mathrm{d}t$$

(15)

Equation (15) is rearranged for the equivalent primary ripple charge  $\Delta Q_{\rm P}$  and solved as follows:

$$\Delta Q_{\rm P} = \frac{C_{\rm P}}{C_{\rm P}^{\circ}} \int_{0}^{\frac{T_{\rm sw}}{M} (Md - \lfloor Md \rfloor)} \left( \sum_{j=1}^{M} -i_{\rm C_{\rm P}}^{\circ}(t) \right) \cdot \mathrm{d}t$$

$$= \frac{1}{M} \int_{0}^{\frac{T_{\rm sw}}{M} (Md - \lfloor Md \rfloor)} \left( \overline{I}_{\rm L} \left( \lfloor Md \rfloor + 1 \right) - M\overline{I}_{\rm P} \right) \cdot \mathrm{d}t$$

$$= \frac{\overline{I}_{\rm P}}{f_{\rm sw}M} \left( 1 - \frac{\lfloor Md \rfloor}{Md} \right) \left( 1 + \lfloor Md \rfloor - Md \right) \tag{16}$$

Comparing (16) with (11), it can be seen these are identical if substituting N by M. If either N converter phases are interleaved or M modules are cascaded, in both cases the same overall size of the DC bus capacitor will be needed. The interleaved topology, however, will result in smaller supercapacitor current ripple or equivalently, smaller inductors.

## IV. LOSS MODEL

This section focuses on the modelling of the converter losses. This is critical for power density optimization, as the converter losses have a direct impact on the weight of the cooling system.

## A. Semiconductor losses

The semiconductor loss model that will be used is specific to MOSFETs. To calculate the conduction losses in the highside and low-side device, the RMS currents as well as the onstate resistance  $R_{\rm DS}$  are needed. Furthermore, for reducing conduction losses it might be useful to parallel multiple pMOSFETs to reduce the equivalent on-state resistance. In the high-side and the low-side MOSFETs, respectively, the following conduction losses occur, which are defined in a universal form, as valid for interleaved and cascaded structures:

$$P_{\rm cond,HS} = NMp \cdot R_{\rm DS} \cdot \left(\frac{I_{\rm HS}^{\circ}}{p}\right)^2 \tag{17}$$

$$P_{\rm cond,LS} = NMp \cdot R_{\rm DS} \cdot \left(\frac{I_{\rm LS}^{\circ}}{p}\right)^2 \tag{18}$$

As the supercapacitor current  $\overline{I}_{L}$  is shared by N phases, conduction losses are reduced for interleaving as the device current reduces. The same is achieved when p devices are paralleled as this will reduce its equivalent resistance. On the other hand, if M converter stages are cascaded, the current has to flow through a multiple M devices and the conduction losses will increase. The power which is required to drive all 2NMp MOSFETs is derived using the total gate charge  $Q_{\rm G}$  and the gate-drive voltage  $V_{\rm G}$ :

$$P_{\rm G} = 2NMp \cdot f_{\rm sw} \cdot Q_{\rm G} V_{\rm G} \tag{19}$$

Calculating the switching losses is a more complex procedure. The device currents at the switching instants are known from (6). For obtaining the switching energies, there are several approaches [12]. In this work, it is assumed that information on the switching energies are available in the manufacturer's datasheets. The switching energies are given as a function of current and voltage  $E_{on}\{I,V\}$ ,  $E_{off}\{I,V\}$ . Those graphs are digitalized and lookup tables are generated to calculate the losses during the switching transitions.

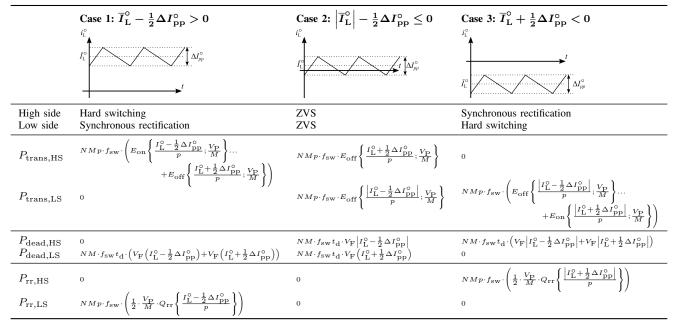

For the switching losses, three cases have to be distinguished, depending on the DC component of the inductor current  $\overline{I}_{L}^{\circ}$ . For low DC current or high ripple, ZVS can be achieved, which is used in many designs [5, 7, 16]. The switching losses consist of three components: First, the losses during the actual switching transitions in the low-side and high-side MOSFETs are denoted  $P_{\text{trans,LS}}$  and  $P_{\text{trans,HS}}$ . Second, during the dead-time  $t_{d}$ , the antiparallel diodes of the MOSFETs cause dead-time losses  $P_{\text{dead,LS}}$  and  $P_{\text{dead,HS}}$ due to their forward voltage drop  $V_{\text{F}}$ . Last, in hard-switching, the antiparallel diodes additionally cause reverse recovery losses  $P_{\text{tr,LS}}$  and  $P_{\text{rr,HS}}$ . All of these loss components are summarized in Table I.

#### B. Losses in passive components

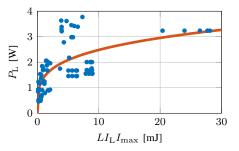

The losses in the inductors are difficult to calculate, as it is not possible to directly derive all geometry variables of an inductor from the given converter variables [17]. Therefore, another approach is chosen.

The so-called area product  $A_p$  of an inductor is used, which is defined as the product of core area  $A_c$  and winding window area  $A_w$ , as it relates to the inductor size. The window area in terms of the copper fill factor  $k_u$ , the current density  $J_{max}$ and the maximum RMS current  $I_L$ , and the core area depends on the peak flux linkage  $LI_{max}$  and maximum flux density  $B_{max}$ . Based on these, the area product is found [17]:

$$A_{\rm p} = A_{\rm c}A_{\rm w} = \frac{LI_{\rm L}I_{\rm max}}{k_{\rm u}B_{\rm max}J_{\rm max}}$$

(20)

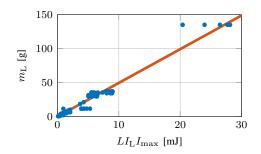

The nominator  $LI_{\rm L}I_{\rm max}$  of (20) only contains data which are available in the datasheets of most inductors. The quantity  $LI_{\rm L}I_{\rm max}$ , although having the unit of an energy, relates to the area product  $A_{\rm p}$ . Therefore, data of inductors manufactured by several companies specialized in magnetics for switchedmode converters have been researched. As large inductors are capable of dissipating higher losses than small inductors, the correlation of the inductor losses  $P_{\rm L}$  that result in a 40 K temperature rise with the quantity  $LI_{\rm L}I_{\rm max}$  can be used to estimate the losses. In Fig. 8, a function to enable the loss estimation is derived.

If the maximum inductor temperature is denoted  $\hat{T}_{\rm L}$  and the ambient  $T_{\rm amb}$ , the losses of the inductors may be obtained via curve fitting as depicted by the red curve in Fig. 8. The temperature rise is scaled linearly:

$$P_{\rm L} \approx MN \cdot \frac{T_{\rm L} - T_{\rm amb}}{40 \,\mathrm{K}} \cdot 7.88 \, \frac{\mathrm{W}}{\mathrm{J}^{0.25}} \left( LI_{\rm L}^{\circ} \left( \left| \overline{I}_{\rm L}^{\circ} \right| + \frac{1}{2} \Delta I_{\rm pp}^{\circ} \right) \right)^{0.25}$$

$$(21)$$

Figure 8: Inductor losses as a function of the area-product related quantity  $LI_{\rm L}I_{\rm max}$ . Manufacturer data and curve fit

One downside of this approach is that high-frequency loss components, such as skin and proximity effect related losses, as well as iron losses are not included. The skin and the proximity effect are not easily accessible analytically [17, 18].

The losses in the DC bus capacitor are assumed to be negligibly small. However, if those losses are to be considered, the RMS current in the DC bus capacitor  $I_{\rm CP}$  as presented in [6, 10] is needed. For the desired capacitor technology, the dissipation factor  $\tan \delta$  may be researched to obtain the equivalent series resistance. Using the RMS current and the equivalent series resistance, the losses can be calculated.

## V. WEIGHT MODEL

This section attempts to calculate the weights of the converter components. For the losses, which influence the weight of the cooling system, the approach of [12] is chosen: Literature [19] states that for a cooling system, the thermal resistance  $R_{\rm th}$  and the weight  $m_{\rm th}$  of a heatsink are linked to a material constant, the thermal figure of merit  $FOM_{\rm th}$ :

$$FOM_{\rm th} = \frac{1}{R_{\rm th} \cdot m_{\rm th}} = \text{const.}$$

(22)

Attempting to optimize the geometry of a heatsink and a fan for minimum weight is a complex procedure which is given in [20, 21]. From the results, it is derived that a thermal figure of merit of  $FOM_{\rm th} = 15 \frac{\rm W}{\rm kg\,K}$  is a reasonable choice for aluminum.

The inductor weight is found by analyzing its correlation with the area product  $A_p$ , using the already collected inductor data. In Fig. 9, the weight  $m_L$  is plotted as a function of the area-product related quantity  $LI_LI_{max}$ . It is found that a linear relationship between  $LI_LI_{max}$  and the weight can be assumed:

$$m_{\rm L} \approx MN \cdot 4.96 \, \frac{\rm kg}{\rm J} \cdot \left( LI_{\rm L}^{\circ} \left( \left| \overline{I}_{\rm L}^{\circ} \right| + \frac{1}{2} \Delta I_{\rm pp}^{\circ} \right) \right)$$

(23)

Finally, for capacitors, the energy density is the central criterion to account for the weight [12, 22]. For ceramic capacitors, an energy density of  $41 \frac{J}{kg}$  is assumed [12]. Equation (13) should be used to calculate the capacitor energy.

Figure 9: Inductor weight as a function of the area-product related quantity  $LI_LI_{max}$ . Manufacturer data and curve fit

In addition to the weights of these components which depend on design choices, a constant part to account for the power stage, PCB, driver circuitry, sensors, screws and connectors is assumed. These components are listed in Table II.

Table II: List of converter hardware components and their weight

| Component                    | Weight each                                                                                | Quantity needed     |

|------------------------------|--------------------------------------------------------------------------------------------|---------------------|

| PCB material (FR4, 4 layers) | $\begin{array}{c} 6 \; \frac{\mathrm{kg}}{\mathrm{m}^2} \\ 2.50 \; \mathrm{g} \end{array}$ | 160 mm x 100 mm     |

| Gate driver circuitry        | 2.50 g                                                                                     | $2 \cdot M \cdot N$ |

| Current sensors              | 7.50 g                                                                                     | M                   |

| Voltage sensors              | 2.50 g                                                                                     | M + 1               |

| Mounting material            | 20 g                                                                                       | 1                   |

## VI. OPTIMIZATION ALGORITHM

In order to find a good initial design for the projected synchronous buck converter for the aircraft supercapacitor system, the analytical models presented in the previous sections are implemented in a MATLAB design algorithm. The parameters to this design procedure are shown in Table III. The goal is to obtain graphs of power density as a function of switching frequency for each of the preselected semiconductor Table III: Simulation parameters of the proposed design algorithm

| Parameter                                       | Typical value                                                           |

|-------------------------------------------------|-------------------------------------------------------------------------|

| Rated input voltage                             | $V_{\rm P} = 270  {\rm V}$                                              |

| Rated power                                     | $\dot{P} = 2 \mathrm{kW}$                                               |

| Number of series-connected supercapacitor cells | $k \in \{32, 64, 96\}$                                                  |

| Simulation at different SOC                     | $V_{\rm S} \in \left[\frac{1}{2}kV_{\rm cell}, \ kV_{\rm cell}\right]$  |

| Range of switching frequency                    | $f_{\rm sw} \in [50  \rm kHz, 1  MHz]$                                  |

| DC bus ripple voltage amplitude                 | $\Delta V_{\rm P} = 4  {\rm V}$                                         |

| Supercapacitor ripple current                   | $\Delta I_{\rm pp} = 10 \% \cdot \frac{P}{\frac{1}{2}  k V_{\rm cell}}$ |

| Ambient temperature                             | $T_{\rm amb} = 30 ^{\circ}{\rm C}$                                      |

| Thermal FOM                                     | $FOM_{\rm th} = 15  \frac{\rm W}{\rm kg  K}$                            |

| Semiconductor devices                           | GaN Systems GS66508T,                                                   |

|                                                 | GaN Systems GS66516T,                                                   |

|                                                 | Panasonic PGA26E07BA,                                                   |

|                                                 | Wolfspeed C3M0065090J,                                                  |

|                                                 | Rohm SCT3017AL                                                          |

| Maximum inductor temperature                    | $\hat{T}_{\rm L} = 100 ^{\circ}{\rm C}$                                 |

| Capacitor energy density                        | $w_{\rm C_{\rm P}} = 41.3  \frac{\rm J}{\rm kg}$                        |

| Number of interleaved half bridges              | $N \in \{1, 2, 3\}$                                                     |

| Number of cascaded half bridges                 | $M \in \{1, 2, 3\}$                                                     |

| Range of inductance                             | $L \in [L_{\min}, 5 \cdot L_{\min}]$                                    |

devices, primarily SiC and GaN power MOSFETs, mentioned in Table III. Therefore, the algorithm is organized as follows:

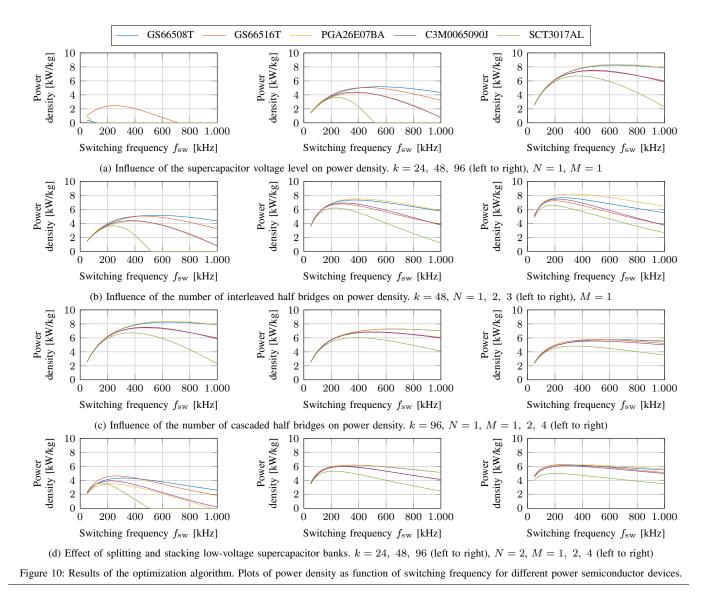

The design inputs are the supercapacitor voltage level k, the number of interleaved half bridges N and the number of cascaded half bridges M. All semiconductor devices are simulated on the whole range of switching frequencies to generate the power density plots as shown in Fig. 10. For each plot, the following procedure is carried out:

For a given semiconductor device and a given switching frequency, the maximum ripple charge is calculated to determine the required primary capacitance  $C_{\rm P}$ , taking into account all possible voltages  $V_{\rm S}$  of the supercapacitor system. Then, the required inductance  $L_{\rm min}$  is calculated based on (9), which guarantees the ripple current  $\Delta I_{\rm pp}$  to stay below the desired

value for all possible supercapacitor voltages  $V_{\rm S}$ . Also higher inductances up to  $5\cdot L_{\rm min}$  are simulated.

Additionally, different numbers of paralleled MOSFETs p are simulated. The minimum and maximum number p is individual for each MOSFET. In this study, a maximum number of 2 paralleled devices is assumed for SMD packages and 1 for bulky leaded packages.

This process is carried out for all possible secondary voltages  $V_{\rm S}$  that correspond to the supercapacitor being fully discharged ( $V_{\rm cell} = 1.25 \,\rm V$ ) to fully charged ( $V_{\rm cell} = 2.50 \,\rm V$ ), for both positive and negative power flow and the lowest value of the power density is saved. This implies that power density is defined when processing the rated power (2 kW) at the most unfavourable operating condition (most likely when the supercapacitor is fully discharged).

The parameters L and p, however, are selected to maximize the power density for a given switching frequency and semiconductor device. After simulating all combinations of switching frequencies and semiconductor devices, the results, such as power density and efficiency graphs, can be plotted.

### VII. RESULTS

In Fig. 10 and Fig. 11, the results from running the design algorithm for the energy storage system specified in section II are presented. Fig. 10 presents the power density graphs and Fig. 11 the respective efficiency profiles. Due to using analytical modelling rather than detailed simulations in time domain, the computation time is significantly shorter. Generating one of the plots requires less than 3 minutes in MATLAB.

First, the influence of the supercapacitor voltage level is analyzed in Fig. 10a and Fig. 11a. The number of seriesconnected supercapacitor cells k is varied from 24 to 96 as introduced in section II. Interleaving and cascading is not regarded. It is clearly visible that higher supercapacitor voltage yields higher power density. This is obviously due to the fact that the current is reduced as voltage increases and therefore, conduction losses decrease. This reflects in the significant increase of the efficiency as seen in Fig. 11a.

In Fig. 10a, it is observed that for the lowest voltage configuration (k = 24), most of the power density graphs are zero. In this case, the losses in the semiconductor devices,

multiplied with the junction-to-case thermal resistance, exceed the maximum allowable temperature rise from the ambient to the maximum junction temperature resulting in an infinite size of the heatsink. This demonstrates that in a low-voltage design, conduction losses are prohibitive.

The benefit of using interleaving can be analyzed at the medium voltage level (k = 48) as illustrated in Fig. 10b and Fig. 11b. The number of interleaved half bridges is increased from N = 1 to N = 3. It can be seen that the power density significantly increases as N increases, whereas the efficiency profiles only increase moderately. As the inductor ripple current  $\Delta I_{\rm pp}^{\circ}$  can be significantly increased compared to the output current ripple  $\Delta I_{\rm pp}$  for N > 1, much weight is saved due to smaller inductors. The increase in efficiency, however, results from the fact that the current is shared between more semiconductors, which is beneficial for conduction losses.

Another interesting observation from Fig. 10b is that the peaks of the power density graphs move toward lower switching frequencies as N increases. This is due to the higher effective switching frequency in interleaved operation, see (2):

As the effective frequency  $f_{\rm sw,eff}$  of the output current ripple increases, the frequency  $f_{\rm sw}$  of the individual phases can be reduced and hence, they operate more efficiently.

The effect of using cascaded cells is analyzed at the highest voltage level k = 96 in Fig. 10c and Fig. 11c. Cascading is analyzed for M = 1, 2, 4. For example, as k = 96 and M = 4, the system consists of 4 series-connected converter cells, each connected to a supercapacitor system working in the range of  $V_{\rm S} = 30 \dots 60$  V. As it was already suspected from equations (17) and (18), the power density decreases with increasing level of cascading. The supercapacitor current flows through more semiconductor devices and therefore, the conduction losses increase as it can be seen in Fig. 11c.

However, having multiple cascaded supercapacitor stacks may be beneficial in terms of redundancy, as already discussed. If a modular design of a supercapacitor bank of the lowest voltage level (k = 24,  $V_S = 30...60$  V) is considered, it is interesting to investigate how the power density changes if more of these modules, e.g. two (k = 48, M = 2) or four (k = 96, M = 4), are connected in series. Additional interleaving of N = 2 is considered. The results are shown in Fig. 10d and Fig. 11d. It can be seen that stacking modules helps to increase power density. In Fig. 11d on the right, abrupt changes in the efficiency profiles can be observed. This is a result from the automatic selection of the number of paralleled devices p. At these points, using less paralleled devices, thus saving the weight of the semiconductors, levels out with the increased cooling effort due to higher losses.

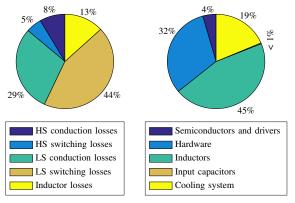

Naturally, more details on the losses and the weight of a specific design may be obtained from the algorithm. As an example, the design with the Panasonic GaN MOSFET PGA26E07BA at 400 kHz, k = 48, N = 2, M = 1 is chosen. This corresponds to the peak power density of Fig. 10b (middle). In Fig. 12, the weight and the loss breakdown are presented. The design reaches a power density of 7.51  $\frac{kW}{kg}$ , which corresponds to a weight of 266 g. The total losses are 79 W, which corresponds to an efficiency of 96.1%. Because of interleaving, the ripple current which flows into the supercapacitor is  $\Delta I_{\rm pp} = 6.67$  A, while the ripple current in each inductor can be increased to  $\Delta I_{\rm pp}^{\circ} = 13.2$  A. Two inductors of 12.7 µH each are needed.

Figure 12: Left: Loss breakdown of the example design (79 W total losses, 96.1% efficiency). Right: Weight breakdown (total 266 g, 7.51  $\frac{kW}{k\sigma}$ )

This design methodology can be further developed to implement a multidimensional optimization algorithm which sometimes exhibits contradicting effects such as lowering weight and maximising efficiency. If, in the example design, the switching frequency is reduced from 400 kHz to 200 kHz, it can be seen from Fig. 10b that the power density will decrease by 8% (from 7.51  $\frac{kW}{kg}$  to 6.91  $\frac{kW}{kg}$ ). However, the converter efficiency improves by 1% according to Fig. 11b. This improves the roundtrip efficiency of the energy storage system by 2%, reducing fuel consumption by more than the added converter weight.

## VIII. CONCLUSION

In this paper, a design procedure for a synchronous buck converter for an aircraft supercapacitor system is presented, which enables the maximization of power denstiy. Two topology variants of the converter that have the capability to increase power density and redundancy, essential in aircaft applications, are considered, namely interleaving and cascading. The proposed design procedure is based on fully analytical modelling of the electrical converter parameters, the losses and the weights of the converter components. This allows to implement this design algorithm very computationally efficient in MATLAB. The generated power density graphs are a useful basis for shortlisting the best converter design configurations.

## ACKNOWLEDGMENT

#### REFERENCES

- P. Wheeler and S. Bozhko. 'The More Electric Aircraft: Technology and challenges.' In: *IEEE Electrification Magazine* 2.4 (2014), pp. 6–12.

- [2] P. Wheeler. 'Technology for the more and all electric aircraft of the future'. In: IEEE International Conference on Automatica (ICA-ACCA). 2016, pp. 1–5.

- [3] A. Sewergin et al. 'Modular bidirectional full-SiC DC-DC converter for automotive applications'. In: *IEEE International Conference on Power Electronics and Drive Systems (PEDS)*. 2017, pp. 277–281.

- [4] M. Pavlovský et al. 'Assessment of Coupled and Independent Phase Designs of Interleaved Multiphase Buck/Boost DC/DC Converter for EV Power Train'. In: *IEEE Transactions on Power Electronics* 29.6 (2014), pp. 2693–2704.

- [5] J. B. Baek et al. 'Digital Adaptive Frequency Modulation for Bidirectional DC/DC Converter'. In: *IEEE Transactions on Industrial Electronics* 60.11 (2013), pp. 5167–5176.

- [6] M. Gerber et al. 'Interleaving optimization in synchronous rectified DC/DC converters'. In: *IEEE Annual Power Electronics Specialists Conference (PESC)*. Vol. 6. 2004, 4655–4661 Vol.6.

- [7] B. Cougo et al. 'High Current Ripple for Power Density and Efficiency Improvement in Wide Bandgap Transistor-Based Buck Converters'. In: *IEEE Transactions* on Power Electronics 30.8 (2015), pp. 4489–4504.

- [8] M. Delhommais et al. 'Using design by optimization for reducing the weight of a SiC switching cell'. In: *IEEE Energy Conversion Congress and Exposition* (ECCE). 2016, pp. 1–8.

- [9] C. Chang and M. A. Knights. 'Interleaving technique in distributed power conversion systems'. In: *IEEE Transactions on Circuits and Systems I* 42.5 (1995), pp. 245–251.

- [10] T. Hegarty. Benefits of multiphasing buck converters. Ed. by EETimes Online. 2007. URL: https://www.eetimes.com/document.asp?doc\_id=1273224.

- [11] X. Yang et al. Analysis and validation of the output current ripple in interleaved buck converter'. In: Annual Conference of the IEEE Industrial Electronics Society (IECON). 2017, pp. 846–851.

- [12] N. Fritz et al. 'Analytical modelling and power density optimisation of a single phase dual active bridge for aircraft application'. In: 9th International Conference on Power Electronics, Machines and Drives (PEMD). 2018.

- U.S. Department of Defense. Interface Standard Mil-Std-704F. Aircraft electric power characteristics. 2004.

- [14] A. Stippich et al. 'Key components of modular propulsion systems for next generation electric vehicles'. In: CPSS Transactions on Power Electronics and Applications 2.4 (2017), pp. 249–258.

- [15] Plexim GmbH. PLECS. The Simulation Platform for Power Electronics. User Manual Version 4.1. 2018.

- [16] J. Zhang et al. 'High-Power Density Design of a Soft-Switching High-Power Bidirectional DC/DC Converter'. In: *IEEE Transactions on Power Electronics* 22.4 (2007), pp. 1145–1153.

- [17] W. G. Hurley and W. H. Woelfle. Transformers and Inductors for Power Electronics. Theory, Design and Applications. Ed. by Wiley. 2013.

- [18] W. G. Hurley et al. 'Optimizing the AC resistance of multilayer transformer windings with arbitrary current waveforms'. In: *IEEE Transactions on Power Electronics* 15.2 (Mar. 2000), pp. 369–376.

- [19] T. Icoz and M. Arik. 'Light Weight High Performance Thermal Management With Advanced Heat Sinks and Extended Surfaces'. In: *IEEE Transactions on Components and Packaging Technologies* 33.1 (Mar. 2010), pp. 161–166.

- [20] C. Gammeter et al. 'Weight Optimization of a Cooling System Composed of Fan and Extruded-Fin Heat Sink'. In: *IEEE Transactions on Industry Applications* 51.1 (2015), pp. 509–520.

- [21] P. Ning et al. 'Selection of heatsink and fan for high-temperature power modules under weight constraint'. In: Twenty-Third Annual IEEE Applied Power Electronics Conference and Exposition. 2008.

- [22] W. J. Sarjeant et al. 'Capacitors'. In: *IEEE Transactions on Plasma Science* 26.5 (1998), pp. 1368–1392.